# onsemi

# **SEPIC Converter Analysis and Design**

# AND90136/D

# Introduction

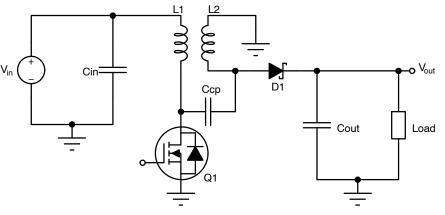

The single–ended primary–inductor converter (SEPIC) is a type of DC/DC converter that allows the electrical potential (voltage) at its output to be greater than, less than, or equal to that at its input. The SEPIC converter is controlled by the duty cycle of the main switch Q1.

Like other DC–DC switch–mode power supply converters, the SEPIC exchanges energy between inductors and capacitors to convert from one voltage to another voltage. Typical applications for a SEPIC regulator are [1]:

• Battery–operated equipment and handheld devices

- NiMH chargers

- LED lighting applications

- DC power supplies having a wide range of input voltages Any boost controller (External FET) or converter

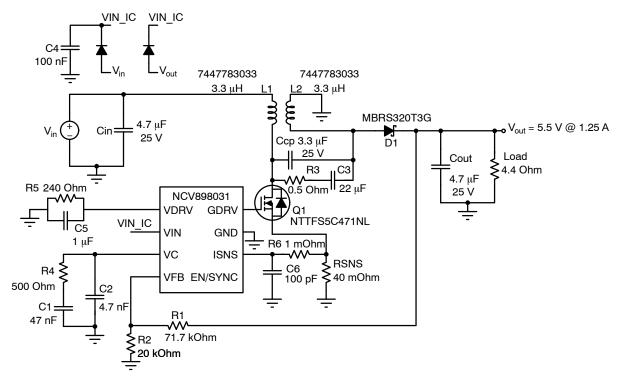

(Internal FET) can be used to control a SEPIC regulator. We will focus on a SEPIC controller for the rest of this document. In figure (1) we have represented the SEPIC controller with separate inductors, however these inductors can be coupled inductors (see <u>Appendix A</u>). A simplified schematic for a SEPIC regulator is shown in figure (1).

Figure 1. SEPIC Converter

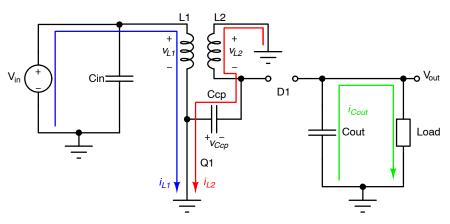

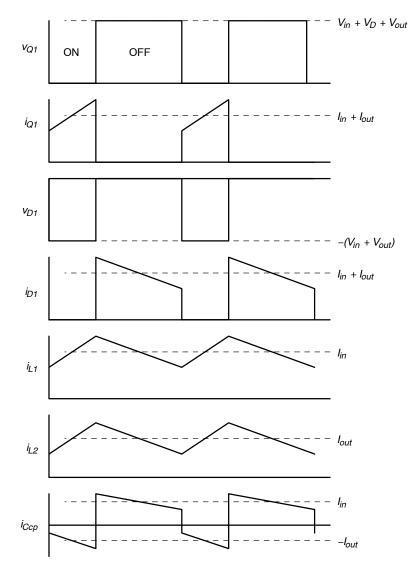

When transistor Q1 is conducting, the input inductor L1 is charged by the input voltage  $V_{in}$ . Inductor L2 takes energy from the coupling capacitor Ccp. The output current to the

load is supplied by capacitor Cout. The simplified schematic while Q1 is conducting (ON state) is shown below in figure (2).

Figure 2. SEPIC Converter during ON State

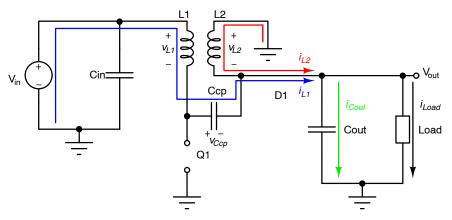

Depicted below in figure (3) is the simplified schematic when transistor Q1 is off. When the main switch Q1 is off, the diode is conducting and inductor L1 charges the coupling

capacitor Ccp. The currents through inductor L1 and inductor L2 provide current to the output capacitor Cout and the load.

# **Duty Cycle**

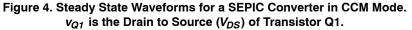

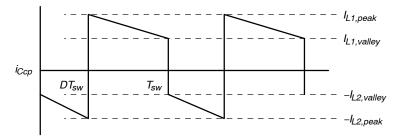

The voltage across inductor L1 (assuming no Ohmic losses in the inductor) is shown below in figure (5):

# Figure 5. Voltage across Inductor L1

Therefore:

Applying Volt–Second balance on inductor L1 we arrive at:

$$\frac{1}{\mathsf{T}_{sw}} \begin{bmatrix} \mathsf{D}\mathsf{T}_{sw} & \mathsf{T}_{sw} \\ \int_{0}^{\mathsf{T}_{sw}} \mathsf{V}_{in} dt + \int_{\mathsf{D}\mathsf{T}_{sw}}^{\mathsf{T}_{sw}} (\mathsf{V}_{in} - \mathsf{V}_{\mathsf{Ccp}} - \mathsf{V}_{\mathsf{D}} - \mathsf{V}_{out}) dt \end{bmatrix} = 0$$

$$= \mathsf{D}\mathsf{T}_{sw}\mathsf{V}_{in} + (1 - \mathsf{D})\mathsf{T}_{sw}(\mathsf{V}_{in} - \mathsf{V}_{\mathsf{Ccp}} - \mathsf{V}_{\mathsf{D}} - \mathsf{V}_{out}) \quad (eq. 1)$$

Given that the average voltage across inductors L1 and L2 equals 0, the average voltage across the coupling capacitor  $V_{Ccp} = V_{in}$ . Replacing  $V_{Ccp}$  with  $V_{in}$  in equation (1) yields:  $DV_{in} + (1 - D)(-V_D - V_{out}) = 0$

$$\frac{D}{1-D} = \frac{V_{out} + V_D}{V_{in}}$$

(eq. 2)

Or:

$$D = \frac{V_{out} + V_D}{V_{in} + V_{out} + V_D}$$

(eq. 3)

Where  $V_D$  is the diode forward voltage. From equation (3) we notice that the maximum duty cycle occurs at  $V_{in(min)}$  and the minimum duty cycle occurs at  $V_{in(max)}$ . If we ignore the diode drop, we arrive at the ideal duty cycle for the regulator:

$$\mathsf{D}_{\mathsf{ideal}} = \frac{\mathsf{V}_{\mathsf{out}}}{\mathsf{V}_{\mathsf{in}} + \mathsf{V}_{\mathsf{out}}} \tag{eq. 4}$$

# **Relationship between Input and Output Current**

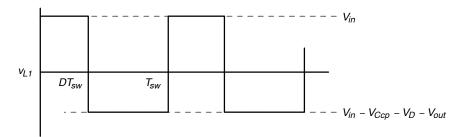

Figure 6. Capacitor Ccp, Currents

When Q1 is conducting, the coupling capacitor Ccp discharges through L2 therefore the capacitor current varies from  $-I_{L2,valley}$  to  $-I_{L2,peak}$  as shown in figure (6). Similarly, when Q1 is off and the diode is conducting, the current

through the coupling capacitor Ccp varies from  $I_{L1,peak}$  to  $I_{L1,valley}$  as shown in figure (6). Applying Ampere second balance on capacitor Ccp yields:

$$\begin{split} \frac{1}{T_{sw}} & \left[ \int_{0}^{DT_{sw}} - \left( I_{L2,valley} + \frac{di_{L2}}{dt} \left( t - 0 \right) \right) dt + \int_{DT_{sw}}^{T_{sw}} \left( I_{L1,peak} - \frac{di_{L1}}{dt} \left( t - DT_{sw} \right) \right) dt \right] = 0 \\ & = \frac{1}{T_{sw}} \left[ \int_{0}^{DT_{sw}} - \left( I_{L2,valley} + \frac{V_{in}}{L_2} t \right) dt + \int_{DT_{sw}}^{T_{sw}} \left( I_{L1,peak} - \frac{V_{out}}{L_1} \left( t - DT_{sw} \right) \right) dt \right] \\ & = \frac{1}{T_{sw}} \left[ \int_{0}^{DT_{sw}} - \left( I_{L2,valley} + \frac{V_{in}}{L_2} t \right) dt + \int_{DT_{sw}}^{T_{sw}} \left( \underbrace{ I_{L1,valley} + \frac{V_{in}}{L_1} DT_{sw}}_{I_{L1,peak}} - \frac{D}{1 - D} \frac{V_{in}}{L_1} \left( t - DT_{sw} \right) \right) dt \right] \\ & = -DT_{sw} \left( I_{L2,valley} + \frac{V_{in}DT_{sw}}{2L_2} \right) + (1 - D)T_{sw} \left( I_{L1,valley} + \frac{V_{in}DT_{sw}}{2L_1} \right) \\ & = -DT_{sw} \left( I_{L2,valley} + \frac{I_{L2,p2p}}{2} \right) + (1 - D)T_{sw} \left( I_{L1,valley} + \frac{I_{L1,p2p}}{2} \right) \right) \end{aligned}$$

(eq. 5) we peak to peak inductor current.

$i = \int \frac{1}{L} v_{L1} dt$

Where  $I_{L,p2p}$  is the peak to peak inductor current.

From equation (5),  $\left(I_{L2,valley} + \frac{I_{L2,p2p}}{2}\right)$  is equal to the average current through inductor L2  $(I_{L2})$ . Following the same approach for inductor L1 we conclude that  $\left(I_{L1,valley} + \frac{I_{L1,p2p}}{2}\right)$  is the average current through inductor L1 ( $I_{L1}$ ). Therefore:  $-DI_{L2} + (1 - D)I_{L1} = 0$

$\frac{I_{L1}}{I_{L2}} = \frac{D}{1 - D}$ (eq. 6)

At this point we have found a relationship between the average inductor currents. Assuming 100% efficiency we arrive at the following expression:

$$V_{out}I_{out} = V_{in}I_{in}$$

$$\frac{V_{out}}{V_{in}} = \frac{I_{in}}{I_{out}} = \frac{I_{L1}}{I_{L2}} = \frac{D_{ideal}}{1 - D_{ideal}}$$

(eq. 7)

Using equation (2) and (7) the relationship between the average input and output currents can be expressed as:

$$I_{in} = I_{out} \frac{D_{ideal}}{1 - D_{ideal}} = I_{out} \frac{V_{out}}{V_{in}}$$

(eq. 8)

#### Inductor selection

When Q1 is conducting, the voltage across the inductor L1 equals:

$$v_{L1} = L_1 \frac{di_{L1}}{dt}$$

(eq. 9)

Using KVL and assuming zero loss in MOSFET Q1, we arrive at the following expression:

(eq. 10)

$$i = \frac{V_{IN}}{L_1}t + I_{L1,valley}$$

(eq. 11)

Equation (9) attains its maximum when  $t = DT_{sw}$  thus:

$$I_{L1,peak} = \frac{V_{IN}}{L_1} DT_{sw} + I_{L1,valley}$$

(eq. 12)

Now the peak-to-peak current can be calculated as

$$\begin{split} I_{L1,p2p} &= I_{L1,peak} - I_{L1,valley} \\ &= \frac{V_{IN}D}{L_1f_{sw}} \end{split} \tag{eq. 13}$$

Where  $f_{sw}$  is the switching frequency of the regulator and is defined as:

$$f_{sw} = \frac{1}{T_{sw}}$$

(eq. 14)

To design the SEPIC regulator we need to define the maximum allowed ripple in the inductors. A good rule of thumb is to use 20% to 40% of the input current. Assuming the allowed ripple through both inductors is 20% we arrive at the following expression:

$$\Delta I_{L} = I_{L1,p2p} = I_{in} \times 20\%$$

(eq. 15)

Solving equation (15) in terms of the output current  $I_{out}$  yields:

$$\Delta I_{L} = I_{out} \frac{V_{out}}{V_{in(min)}} \times 20\%$$

(eq. 16)

Using equation (13), the inductor value can be calculated as:

$$L_1 = L_2 = L = \frac{V_{in(min)}}{\Delta I_L f_{sw}} D_{max} \qquad (eq. 17)$$

If inductors L1 and L2 are coupled inductors, the value of the inductance required is half of what would be needed should there be two separate inductors [2]. Therefore, for coupled inductors the value of inductance required is given by:

$$L_{1a} = L_{1b} = \frac{V_{in,min}}{2\Delta I_{L} f_{S}} D_{max}$$

(eq. 18)

The peak current in inductor L1 can be expressed as:

AL.

$$I_{L1,peak} = I_{L1} + \frac{\Delta I_L}{2}$$

(eq. 19)

$$= I_{in} + \frac{\Delta L}{2}$$

$$= I_{out} \frac{1 - D_{max}}{1 - D_{max}} + \frac{1}{2}$$

$$= I_{out} \frac{D_{max}}{1 - D_{max}} \times \left(1 + \frac{20\%}{2}\right)$$

(eq. 20)

Or in terms of the input and output voltages:

$$= I_{out} \frac{V_{out} + V_D}{V_{in(min)}} \times \left(1 + \frac{20\%}{2}\right)$$

(eq. 21)

Similarly, the peak current in inductor L2 can be expressed as:

$$I_{L2,peak} = I_{L2} + \frac{\Delta I_L}{2}$$

(eq. 22)

$$= I_{out} + \frac{\Delta_L}{2}$$

$$= I_{out} \times \left(1 + \frac{20\%}{2}\right)$$

(eq. 23)

The minimum or valley currents through L1 and L2 inductors can be defined as:

$$I_{L1,valley} = I_{in} - \frac{\Delta I_L}{2}$$

(eq. 24)

$$I_{L2,valley} = I_{out} - \frac{\Delta I_L}{2}$$

(eq. 25)

#### **Power MOSFET Selection (External FET)**

The current through transistor Q1 is the sum of the inductor currents while Q1 is conducting

$$\begin{split} i_{Q1}(t) &= i_{L1}(t) + i_{L2}(t) & (eq. 26) \\ &= I_{L1,valley} + \frac{V_{IN}}{L}t + I_{L2,valley} + \frac{V_{in}}{L}t \\ &= I_{L1,valley} + I_{L2,valley} + \frac{2V_{in}}{L}t & (eq. 27) \end{split}$$

The maximum or peak current through the transistor can be defined as:

$$I_{Q1,peak} = I_{L1,peak} + I_{L2,peak}$$

(eq. 28)

The RMS current through transistor Q1 can be defined as [3]:

$$I_{Q1,rms} = \sqrt{\frac{1}{T_{sw}} \int_{0}^{T_{sw}} i_{Q1}^{2}(t)} = \sqrt{\frac{1}{T_{sw}} \int_{0}^{T_{sw}} \left( I_{IL1,valley} + I_{L2,valley} + \frac{2V_{in}}{L} t \right)^{2}}$$

$$= \sqrt{(I_{IL1,valley} + I_{L2,valley})^{2} D_{max} + (I_{L1,valley} + I_{L2,valley}) \frac{2V_{in}}{L} D_{max}^{2} T_{sw} + V_{in(min)}^{2} \frac{4}{L^{2}} \frac{D_{max}^{3} T_{sw}^{2}}{3}}{3}}$$

After some algebraic manipulation, the equation for the RMS current is given by:

$$I_{Q1,rms} = \sqrt{D_{max} \left[ \left( \frac{1}{1 - D_{max}} I_{out} \right)^2 + \frac{1}{3} V_{in(min)}^2 \frac{1}{L^2} \frac{D_{max}^2}{f_{sw}^2} \right]}$$

(eq. 30)

Though less accurate, for a quick, back of the envelope calculation, we can ignore the second summand in the expression above which yields:

$$I_{Q1,rms} = \sqrt{D_{max} \left[ \left( \frac{1}{1 - D_{max}} I_{out} \right)^2 \right]}$$

$$= \frac{I_{out}}{(1 - D_{max})} \sqrt{D_{max}}$$

$$= \frac{I_{in}}{\sqrt{D_{max}}}$$

(eq. 31)

Or in terms of the input and output voltages:

$$I_{Q1,rms} = I_{out} \sqrt{\frac{(V_{in(min)} + V_{out} + V_D)(V_{out} + V_D)}{V_{in(min)}^2}}$$

(eq. 32)

(eq. 29)

The power losses in the transistor Q1 can be divided into two categories:

- 1. Conduction Losses

- 2. Switching or overlap Losses

The total power losses in transistor Q1 are equal to:

$$P_{Q1} = P_{cond} + P_{sw}$$

(eq. 33)

The conduction losses in the transistor is given by:

$$P_{\text{Cond}} = I_{\text{Q1,rms}}^2 r_{\text{DS(ON)}} D_{\text{max}}$$

(eq. 34)

The switching losses are approximately equal to,

$$P_{sw} = \frac{1}{2} V_{DS} I_{Q1,peak} (\tau_{rise} + \tau_{fall}) f_{sw}$$

(eq. 35)

When Q1 is off, the voltage from drain to source can be calculated using a KVL:

$$V_{DS} = V_{Ccp} + V_D + V_{out}$$

(eq. 36)

Given,

$V_{Ccp} = V_{in(max)}$

Equation (36) can be expressed as,

$$V_{DS} = V_{in(max)} + V_D + V_{out}$$

(eq. 37)

Therefore

Therefore,

$$P_{sw} = \frac{1}{2} (V_{in(max)} + V_D + V_{out}) I_{Q1,peak} (\tau_{rise} + \tau_{fall}) f_{sw} \quad (eq. 38)$$

Where  $\tau_{rise} \& \tau_{rise}$  are the rise and fall of the gate of Q1 and can be calculated as,

$$\tau_{rise} = \frac{Q_{gd}}{I_{src}}$$

(eq. 39)

$$\tau_{fall} = \frac{Q_{gd}}{I_{snk}} \tag{eq. 40}$$

$Q_{gd}$  is the MOSFET Miller plateau voltage gate charge, and  $I_{src}$  and  $I_{snk}$  are the source and sink currents of the gate driver respectively. The  $r_{DS(ON)}$  is typically found in the datasheet and should be selected at maximum junction temperature. To ensure proper operation, the selected MOSFET must have:

- 1. Breakdown voltage >  $V_{in(max)} + V_D + V_{out}$

- 2. Continuous current capability >  $I_{Q1(rms)}$

- 3. Maximum junction temperature  $T_{j(max)} > P_{Q1} x$

- $R_{\theta JA} + T_{ambient}$

- 4.  $V_{GS}$  > Gate drive voltage

It is important to mention that if a SEPIC converter is used (internal FET)  $I_{Q1(rms)}$  will be the maximum current through the device.

$$I_{Ccp,rms,max} = \sqrt{\frac{1}{T_{sw}} \int_{0}^{T_{sw}} i_{Ccp}^{2}(t)} \approx \sqrt{\frac{1}{T_{sw}} \int_{0}^{T_{sw}} i_{Ccp}^{2}(t)} \approx \sqrt{\frac{1}{T_{sw}} \int_{0}^{T_{sw}} i_{Ccp}^{2}(t)}$$

For simplicity we have assumed the average current through the inductors. The RMS current can now be expressed as:

$$I_{Cp,rms,max} = \sqrt{D_{max}I_{L2}^2 + (1 - D_{max})I_{L1}^2}$$

(eq. 46)

Employing equation (6), the expression above can be simplified to:

$$I_{Cp,rms,max} = \sqrt{D_{max}I_{out}^2 + (1 - D_{max}) \left(I_{out} \frac{D_{max}}{1 - D_{max}}\right)^2}$$

$$= I_{out} \sqrt{\frac{D_{max}}{1 - D_{max}}} \qquad (eq. 47)$$

Or in terms of the input and output voltages:

$$= I_{out} \sqrt{\frac{V_{out} + V_D}{V_{in_{min}}}}$$

(eq. 48)

#### **Diode Selection**

To ensure proper operation and avoid damaging the diode, the diode selected must be able to withstand reverse voltages equal to:

$$V_{\rm R} = V_{\rm in(max)} + V_{\rm out(max)}$$

(eq. 41)

The peak current through the diode is equal to the peak current of transistor Q1 so the diode must be able to handle:

$$I_{D(peak)} = I_{Q1,peak} = I_{L1,peak} + I_{L2,peak}$$

(eq. 42)

There's also an average current that the diode must be able to withstand:

$$I_{D} = I_{in} + I_{out} = \frac{I_{out}}{1 - D}$$

(eq. 43)

Last but not least, the conduction loss in the diode is equal to the diode average current times the forward voltage drop in the diode therefore the diode package must be able to dissipate up to:

$$P_D = I_D V_D (1 - D) = I_{out} V_D$$

(eq. 44)

To improve efficiency (or reduce losses in the diode) a diode with a low forward voltage is recommended. Schottky diodes are a good candidate due to their low forward voltage.

In summary, for proper operation the selected diode must have:

- 1. Reverse voltage capability  $\geq V_{in(max)} + V_{out(max)}$

- 2. Peak current capability  $\geq I_{Q1(peak)}$

- 3. Average current capability  $\geq I_{in} + I_{out}$

- 4. Maximum junction temperature  $T_{j(max)} \ge P_D \ge R_{\theta JA} + T_{ambient}$

### **Coupling Capacitor Selection**

To calculate the amount of RMS that coupling capacitor Ccp must withstand, we need to calculate the RMS current in the capacitor. The RMS current can be calculated as [3]:

$$\approx \sqrt{\frac{1}{T_{sw}} \left[ \int_{0}^{DT_{sw}} I_{L2}^{2} dt + \int_{DT_{sw}}^{T_{sw}} I_{L1}^{2} dt \right]}$$

(eq. 45)

The coupling capacitor must be able to handle voltages equal to:

# V<sub>in(max)</sub>

The peak-to-peak voltage across the capacitor can be calculated as:

$$\begin{split} \Delta V_{Ccp} &= \frac{1}{Ccp} \int_{DT_{sw}}^{T_{sw}} I_{in} dt \\ &= \frac{I_{in}(1 - D_{max})T_{sw}}{Ccp} \\ &= I_{out} \frac{D_{max}}{1 - D_{max}} \frac{(1 - D_{max})T_{sw}}{Ccp} \\ &= \frac{I_{out}D_{max}}{Ccpf_{sw}} \end{split}$$

(eq. 49)

The ripple across the coupling capacitor Ccp, is determined by its capacitance and its equivalent series resistance (ESR). Assuming a linear relationship between the two sources of ripple we arrive at:

$$\Delta V_{Ccp} \leq \frac{I_{out}D_{max}}{Ccpf_{sw}} + ESR \times max(I_{L1,peak}, I_{L2,peak})$$

Thus, the coupling capacitor can be calculated as:

$$Ccp \ge \frac{I_{out}D_{max}}{\Delta V_{Ccp}f_{sw}}$$

(eq. 50)

Similarly, the maximum ESR can be calculated as:

$$\mathsf{ESR} \leq \frac{\Delta \mathsf{V}_{\mathsf{Ccp}}}{\max(\mathsf{I}_{\mathsf{L1},\mathsf{peak}},\mathsf{I}_{\mathsf{L2},\mathsf{peak}})} \tag{eq. 51}$$

It is recommended to use a ceramic capacitor to keep the ESR losses as small as possible.

#### **Output Capacitor Selection**

Looking at figure (4), when transistor Q1 is conducting, the current through the output capacitor equals  $I_{out}$  since the capacitor is the only element providing current to the output. When transistor Q1 is off the current through the Cout is the sum of the inductors L1 and L2 current minus the load current. Assuming average currents for simplicity, the output capacitor RMS current can be expressed as:

$$I_{\text{Cout,rms,max}} = \sqrt{\frac{1}{T_{\text{sw}}} \left[ \int_{0}^{DT_{\text{sw}}} I_{\text{out}}^2 dt + \int_{DT_{\text{sw}}}^{T_{\text{sw}}} (I_{\text{L1}} + I_{\text{L2}} - I_{\text{out}})^2 dt \right]}$$

(eq. 52)

From equation (7)  $I_{out} = I_{L2}$  therefore

$$I_{\text{Cout,rms,max}} = I_{\text{Ccp,rms,max}} = \sqrt{\frac{1}{T_{\text{sw}}} \left[ \int_{0}^{DT_{\text{sw}}} I_{\text{L2}}^{2} dt + \int_{DT_{\text{sw}}}^{T_{\text{sw}}} I_{\text{L1}}^{2} dt \right]}$$

$$I_{\text{Cout,rms}} = I_{\text{out}} \sqrt{\frac{D_{\text{max}}}{1 - D_{\text{max}}}} \qquad (eq. 53)$$

Or in terms of the input and output voltages:

$$= I_{out} \sqrt{\frac{V_{out} + V_D}{V_{IN_{min}}}}$$

(eq. 54)

The ripple across the output capacitor Cout, is determined by its capacitance and its equivalent series resistance (ESR). Assuming a linear relationship between the two sources of ripple we arrive at:

$$\Delta V_{Cout} \leq \frac{I_{out} D_{max}}{Cout f_{sw}} + ESR \times (I_{L1,peak} + I_{L2,peak})$$

Thus, the output capacitor can be calculated as:

$$Cout \ge \frac{I_{out}D_{max}}{\Delta V_{Cout}fsw}$$

(eq. 55)

Similarly, the maximum ESR can be calculated as:

$$\mathsf{ESR} \le \frac{\Delta \mathsf{V}_{\mathsf{Cout}}}{\mathsf{I}_{\mathsf{L1,peak}} + \mathsf{I}_{\mathsf{L2,peak}}} \tag{eq. 56}$$

It is recommended to use a ceramic capacitor to keep the losses small.

# **Input Capacitor**

The input capacitor sees moderately low RMS current thanks to the input inductor. The RMS current in the input capacitor is given by:

$$I_{\text{Cin,rms}} = \frac{\Delta I_{\text{L}}}{\sqrt{12}}$$

(eq. 57)

# **Design Example**

Input voltage: 3.75 – 9.0 V Output voltage: 5.5 V Output current: 1.25 A Frequency: 2 MHz Assuming a diode drop of 0.5 V Temperature: 85°C Device selected **onsemi** <u>NCV898031</u>

# Step 1: Calculate the Duty Cycle

$$D_{max} = \frac{V_{out} + V_D}{V_{in(min)} + V_{out} + V_D}$$

=  $\frac{5.5 + 0.5}{3.75 + 5.5 + 0.5} = 0.6154$

$$D_{min} = \frac{V_{out} + V_D}{V_{in(max)} + V_{out} + V_D}$$

=  $\frac{5.5 + 0.5}{9.0 + 5.5 + 0.5} = 0.4$

# Step 2: Inductor Selection

Calculate the inductor ripple current:

$$\Delta I_{L} = I_{out} \frac{V_{out}}{V_{in(min)}} \times 20\%$$

= 1.25 ×  $\frac{5.5}{3.75}$  × 20% = 0.3667 A

Now the inductance L1 and L2 can be calculated:

$$\begin{split} L_1 &= L_2 = L = \frac{V_{in(min)}}{\Delta I_L f_{sw}} D_{max} \\ &= \frac{3.75}{0.3667 \times 2e6} \times 0.6154 = 3.1469\,\mu\text{H} \end{split}$$

Wurth Elektronik <u>7447783033</u>: 3.3  $\mu$ H, 4.1 A, and 18 m $\Omega$  is selected for L1 and L2. Based on the inductor selected, we can calculate the actual inductor ripple as:

$$\Delta I_{L} = \frac{V_{in(min)}}{Lf_{sw}} D_{max} = 0.3497 \text{ A}$$

Ripple =  $\frac{\Delta I_{L}}{I_{out}} \frac{V_{in(min)}}{V_{out}} \times 100 = 19.07\%$

The peak L1 current can be calculated as:

$$I_{L1,peak} = I_{out} \frac{V_{out} + V_D}{V_{in(min)}} \times \left(1 + \frac{19.07\%}{2}\right)$$

$$= 1.25 \times \frac{5.5 + 0.5}{3.57} \times \left(1 + \frac{19\%}{2}\right) = 2.1907 \text{ A}$$

And the peak L2 current can be calculated as:

$$I_{L2,peak} = I_{out} \times \left(1 + \frac{19.07\%}{2}\right)$$

$$= 1.25 \times \left(1 + \frac{19\%}{2}\right) = 1.3692 \text{ A}$$

### Step 3. Power MOSFET Selection

The peak current through the MOSFET equals:

Calculate the rms current through the MOSFET:

Α

$$I_{Q1(rms)} = \sqrt{D_{max} \left[ \left( \frac{1}{1 - D_{max}} I_{out} \right)^2 + \frac{1}{3} V_{in(min)}^2 \frac{1}{L^2} \frac{D_{max}^2}{F_{sw}^2} \right]}$$

$$= \sqrt{0.6154 \times \left[ \left( \frac{1}{1 - 0.6154} \times 1.25 \right)^2 + \frac{3.75^2}{3} \times \frac{1}{3.3e - 6^2} \times \frac{0.6154^2}{2e6^2} \right]}$$

$$= 2.5544 \text{ A}$$

Breakdown voltage:

$$\begin{split} V_{BDSS} \, &> \, V_{in(max)} \, + \, V_{out} \, + \, V_{D} \\ &> \, 9 \, + \, 5.5 \, + \, 0.5 \\ &> \, 15 \, V \end{split}$$

Assuming an  $r_{DS(ON)}$  of 10 m $\Omega$ , the conduction power dissipation can be calculated:

$$\begin{split} P_{Cond} &= I_{Q1,rms}^2 r_{DS(ON)} D_{max} \\ &= 2.5544^2 \times 10e{-}3 \times 0.6154 \, = \, 40.2 \; mW \end{split}$$

Similarly, assuming a  $\tau_{rise}$  &  $\tau_{fall}$  of 10 ns each, the switching power loss can be calculated:

$$\begin{split} \mathsf{P}_{sw} &= \frac{1}{2} (\mathsf{V}_{out} + \mathsf{V}_{\mathsf{D}} + \mathsf{V}_{in(max)}) \mathsf{I}_{\mathsf{Q1,peak}} (\tau_{rise} + \tau_{fall}) \mathsf{f}_{sw} \\ &= \frac{1}{2} \times 15 \times 3.5599 \times (10e\text{-}9 + 10e\text{-}9) \times 2e6 = 1.0680 \text{ W} \end{split}$$

Now the total power dissipation can be calculated:

$P_{Q1} = P_{cond} + P_{sw}$

$= 40.2e{-}3 + 1.0680 = 1.1081 \text{ W}$

$V_{GS}$  has to be greater than the gate drive voltage for <u>NCV898031</u> which is equal to 6.3 (typ). The <u>onsemi</u> MOSFET <u>NTTFS5C471NL</u> N-Channel, 40 V, 12 A, 9 m $\Omega$ was selected using **onsemi** <u>Product Recommendation</u> <u>Tool+</u>. For <u>NTTFS5C471NL</u>, the  $R_{\theta JA} = 50 \ C/W$  and the  $T_{j(max)} = 175 \ C$  therefore

$$\begin{split} T_{j(max)} &> P_{Q1} \times R_{\theta JA} + T_{ambient} \\ 175 &> 1.1081 \times 50 + 85 \\ 175^{\circ}C &> 140.4^{\circ}C \end{split}$$

#### **Step 4: Diode Selection**

The peak current for the diode is equal to:

The reverse voltage for the diode equals:

= 9.0 + 5.5 = 14.5 V

The average current for the diode equals:

$$I_{\rm D} = \frac{I_{\rm out}}{1 - D_{\rm min}} = \frac{1.25}{1 - 0.4} = 2.0833 \,\text{A}$$

At  $I_D = 2A$  (@ 100 °C), the forward diode drop  $V_D \approx 0.35$ , therefore the power dissipated in the diode equals:

$$P_{D} = I_{out}V_{D}$$

= 1.25 × 0.35 = 0.4375 W

The onsemi Diode MBRS

The **onsemi** Diode <u>MBRS320T3G</u>, Schottky Power Rectifier, Surface Mount, 3.0 A, 20 V is selected. For the selected diode the  $R_{\theta JA} \approx 30 \, ^{\circ}C/W$

$$\begin{split} T_{j(max)} &> P_D \times R_{\theta JA} + T_{ambient} \\ 150 &> 0.4375 \times 30 + 85 = 98.125 \\ 150^{\circ}C &> 103.75^{\circ}C \end{split}$$

# Step 5: SEPIC Coupling Capacitor Selection

The RMS current through the capacitor is given by:

$$I_{Ccp,rms} = I_{out} \sqrt{\frac{V_{out} + V_D}{V_{in_{min}}}}$$

$$= 1.25 \sqrt{\frac{5.5 + 0.5}{3.75}} = 1.5811 \text{ A}$$

For 5% ripple, the minimum capacitance can be calculated as:

$$\begin{split} C_{Ccp} &\geq \frac{I_{out} D_{max}}{0.05 \times V_{in(min)} f_{sw}} \\ &\geq \frac{1.25 \times 0.6154}{0.05 \times 3.75 \times 2e6} \geq 2.05 \, \mu F \end{split}$$

Wurth Elektronik <u>885012209026</u> 3.3  $\mu$ F, 25 V, and 3.69 m $\Omega$  @ 2 MHz is selected for Ccp. Given we have selected a ceramic capacitor with low ESR, we will ignore the ESR requirement.

It may become necessary to place an RC damping network in parallel with the coupling capacitor if the resonance is within ~1 decade of the closed-loop crossover frequency. The capacitance of the damping capacitor should be ~5 times that of the coupling capacitor. The optimal damping resistance (including the ESR of the damping capacitor) is calculated as:

$$R_{damping} = \sqrt{\frac{L1 + L2}{Ccp}}$$

See reference [4] for more details.

# Step 6: Output Capacitor Selection

The RMS current through the capacitor is given by:

$$I_{Cout,rms} = I_{out} \sqrt{\frac{V_{out} + V_D}{V_{in}}}$$

$$= 1.25 \sqrt{\frac{5.5 + 0.5}{3.75}} = 1.5811 \text{ A}$$

For 2% ripple, the minimum capacitance can be calculated as:

$$\begin{split} C_{Cout} &\geq \frac{I_{out} D_{max}}{0.02 \times V_{out} f_{sw}} \\ &\geq \frac{1.25 \times 0.6154}{0.02 \times 5.5 \times 2e6} \geq 3.4965 \, \mu F \end{split}$$

Wurth Elektronik <u>885012208068</u> 4.7  $\mu$ F, 25 V, and 3.73 m $\Omega$  @ 2 MHz is selected for C<sub>out</sub>. Given we have selected a ceramic capacitor with low ESR, we will ignore the ESR requirement.

# **Step 7: Input Capacitor Selection**

The RMS current through the input capacitor is given by Wurth Elektronik <u>885012208068</u> 4.7  $\mu$ F, 25 V, and 3.73 m $\Omega$  @ 2 MHz is selected for Cin.

Selecting the input capacitor needs special considerations such as:

$$I_{Cin,rms} = \frac{\Delta I_L}{\sqrt{12}}$$

$$= \frac{0.3497}{\sqrt{12}} = 0.1 \text{ A}$$

- Electromagnetic Interference (EMI). An EMI filter might be needed to mitigate EMI.

- Negative impedance of the converter. Negative impedance can lead to oscillations.

These items must be addressed in the physical circuit thus it lies beyond the scope of this application report.

# **Simulation Results**

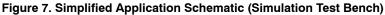

To corroborate our analytical waveforms and ensure proper operation, simulations where carried out using the <u>NCV898031</u> <u>SIMPLIS</u> model and the schematic in figure (7) for the following conditions:

Input voltage: 6.0 V Output voltage: 5.5 V Output current: 1.25 A Frequency: 2 MHz

**Figure 8. Transient Simulation Results**

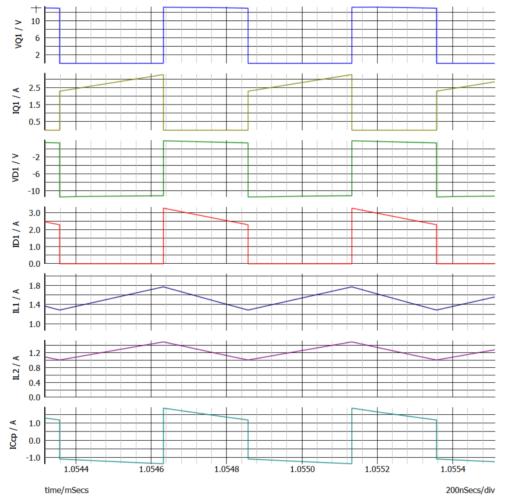

Figure 9. Open Loop Response

There are also more average models that can be downloaded to simulate the loop response of the circuit and measure the stability of the design. All the models can be found on the product page for <u>NCV898031</u> under the technical Documentation & Design Resources:

| Technical Documentation & Design Resources |                                |

|--------------------------------------------|--------------------------------|

| Design & Development Tools (1)             | Videos (1)                     |

| Simulation Models (3)                      | Evaluation Board Documents (5) |

| Data Sheets (1)                            | FAQ (2)                        |

| Package Drawings (1)                       |                                |

# Figure 10.

# **Resources:**

- 1. Find the best product for your application using onsemi Product Recommendation Tool+ (PRT+)

- 2. Simulate the performance for your regulator using **onsemi** <u>WebDesigner+ (WD+)</u>

# **References:**

- [1] Coupled Inductors for SEPIC Converter Applications, https://www.we-online.com/web/en/electronic\_compo\_ nents/news\_pbs/blog\_pbcm/blog\_detail-worldofelectr onics\_77630.php

- [2] onsemi Application note DN06033/D, NCP3065 SEPIC LED Driver for MR16, <u>https://www.onsemi.com/pub/Collateral/DN06033–D.</u> <u>PDF</u>

- [3] Ioinovici, A. (2015). *Power electronics and energy conversion systems: ac.* John Wiley.

- [4] NCV898031 Data sheet, <u>https://www.onsemi.com/pdf/</u> <u>datasheet/ncv898031-d.pdf</u>

### Appendix A

Using coupled inductors leads to a design with better integration, less components, and lower inductance requirement when compared to using two separate inductors. One issue with coupled inductors is that it's harder to find high power off-the-shelf coupled inductors as compared to single inductors.

onsemi, ONSEMI, and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <u>www.onsemi.com/site/pdf/Patent-Marking.pdf</u>. Onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by onsemi. "Typical" parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi does not convey any license under any of its intellectual property rights or the rights of others. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any EDA Class 3 medical devices or medical devices with a same or similar classification. Buyer shall indemnify and hold onsemi and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney feas arising out of, directly or indirectly, any claim of personal injury of death associated with such unintended or unauthori

#### PUBLICATION ORDERING INFORMATION

LITERATURE FULFILLMENT:

#### TECHNICAL SUPPORT

onsemi Website: www.onsemi.com

Email Requests to: orderlit@onsemi.com

North American Technical Support: Voice Mail: 1 800–282–9855 Toll Free USA/Canada Phone: 011 421 33 790 2910 Europe, Middle East and Africa Technical Support: Phone: 00421 33 790 2910 For additional information, please contact your local Sales Representative