# onsemi

## **3 A Output Current, High Speed MOSFET Gate Driver Optocoupler**

# **FOD3182**

#### Description

The FOD3182 is a 3 A Output Current, High Speed MOSFET Gate Drive Optocoupler. It consists of a aluminium gallium arsenide (AlGaAs) light emitting diode optically coupled to a CMOS detector with PMOS and NMOS output power transistors integrated circuit power stage. It is ideally suited for high frequency driving of power MOSFETS used in Plasma Display Panels (PDPs), motor control inverter applications and high performance DC/DC converters.

The device is packaged in an 8-pin dual in-line housing compatible with 260°C reflow processes for lead free solder compliance.

#### Features

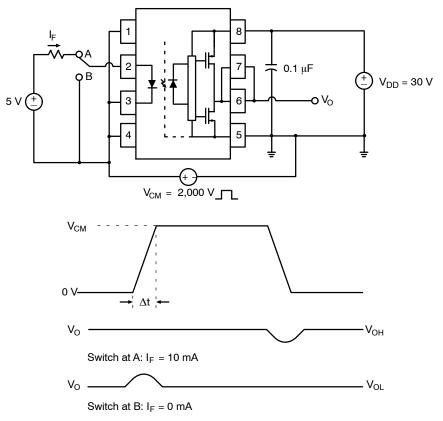

- High Noise Immunity Characterized by 50 kV/µs (Typ.) Common Mode Rejection @  $V_{CM}$  = 2,000 V

- Guaranteed Operating Temperature Range of -40°C to +100°C

- 3 A Peak Output Current

- Fast Switching Speed

- 210 ns Max. Propagation Delay

- 65 ns Max. Pulse Width Distortion

- Fast Output Rise/Fall Time

- Offers Lower Dynamic Power Dissipation

- 250 kHz Maximum Switching Speed

- Wide V<sub>DD O</sub>perating Range: 10 V to 30 V

- Use of P-Channel MOSFETs at Output Stage Enables Output Voltage Swing Close to the Supply Rail (Rail-to-Rail Output)

- 5000 Vrms, 1 Minute Isolation

- Under Voltage Lockout Protection (UVLO) with Hysteresis -Optimized for Driving MOSFETs

- Minimum Creepage Distance of 8.0 mm

- Minimum Clearance Distance of 10 mm to 16 mm (Option TV or TSV)

- Minimum Insulation Thickness of 0.5 mm

- UL and VDE\*

- 1,414 Peak Working Insulation Voltage (V<sub>IORM</sub>) \*Requires "V" Ordering Option

#### Applications

- Plasma Display Panel

- High Performance DC/DC Convertor

- High Performance Switch Mode Power Supply

- High Performance Uninterruptible Power Supply

- Isolated Power MOSFET Gate Drive

#### MARKING DIAGRAM

3182 = Device Number

V = VDE Mark (Note: Only appears on parts ordered with DIN EN/IEC 60747-5-2 option - See ordering table)

- = Two Digit Year Code, e.g., "11" XX

- = Digit Work Week Ranging from "01" to "53" YY

- в = Assembly Package Code

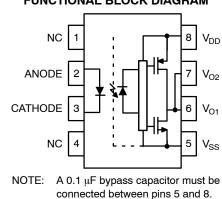

#### FUNCTIONAL BLOCK DIAGRAM

#### **ORDERING INFORMATION**

See detailed ordering and shipping information on page 16 of this data sheet.

#### TRUTH TABLE

| LED | V <sub>DD</sub> – V <sub>SS</sub> "Positive Going" (Turn–on) | V <sub>DD</sub> – V <sub>SS</sub> "Negative Going" (Turn–off) | vo         |

|-----|--------------------------------------------------------------|---------------------------------------------------------------|------------|

| Off | 0 V to 30 V                                                  | 0 V to 30 V                                                   | Low        |

| On  | 0 V to 7.4 V                                                 | 0 V to 7 V                                                    | Low        |

| On  | 7.4 V to 9 V                                                 | 7 V to 8.5 V                                                  | Transition |

| On  | 9 V to 30 V                                                  | 8.5 V to 30 V                                                 | High       |

#### **PIN DEFINITIONS**

| Pin No. | Name            | Description                                                 |

|---------|-----------------|-------------------------------------------------------------|

| 1       | NC              | Not Connected                                               |

| 2       | Anode           | LED Anode                                                   |

| 3       | Cathode         | LED Cathode                                                 |

| 4       | NC              | Not Connected                                               |

| 5       | V <sub>SS</sub> | Negative Supply Voltage                                     |

| 6       | V <sub>O2</sub> | Output Voltage 2 (internally connected to V <sub>O1</sub> ) |

| 7       | V <sub>O1</sub> | Output Voltage 1                                            |

| 8       | V <sub>DD</sub> | Positive Supply Voltage                                     |

**SAFETY AND INSULATION RATINGS** (As per DIN EN/IEC 60747–5–2. This optocoupler is suitable for "safe electrical insulation" only within the safety limit data. Compliance with the safety ratings shall be ensured by means of protective circuits.)

| Symbol                | Parameter                                                                                                                                          | Min.            | Тур.      | Max. | Unit              |

|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----------|------|-------------------|

|                       | Installation Classifications per DIN VDE 0110/1.89 Table 1                                                                                         |                 |           |      | 1                 |

|                       | For Rated Mains Voltage < 150 Vrms                                                                                                                 | -               | I–IV      | -    |                   |

|                       | For Rated Mains Voltage < 300 Vrms                                                                                                                 | -               | I–IV      | -    |                   |

|                       | For Rated Mains Voltage < 450 Vrms                                                                                                                 | -               | I–III     | -    |                   |

|                       | For Rated Mains Voltage < 600 Vrms                                                                                                                 | _               | I–III     | -    |                   |

|                       | For Rated Mains Voltage < 1000 Vrms (Option T, TS)                                                                                                 | _               | I–III     | _    |                   |

|                       | Climatic Classification                                                                                                                            | -               | 40/100/21 | _    |                   |

|                       | Pollution Degree (DIN VDE 0110/1.89)                                                                                                               | _               | 2         | _    |                   |

| CTI                   | Comparative Tracking Index                                                                                                                         | 175             | -         | _    |                   |

| V <sub>PR</sub>       | Input to Output Test Voltage, Method b,<br>$V_{IORM} \times 1.875 = V_{PR}$ , 100% Production Test with tm = 1 second,<br>Partial Discharge < 5 pC | 2651            | -         | -    |                   |

|                       | Input to Output Test Voltage, Method a,<br>$V_{IORM} \times 1.5 = V_{PR}$ , Type and Sample Test with tm = 60 seconds,<br>Partial Discharge < 5 pC | 2121            | -         | _    |                   |

| V <sub>IORM</sub>     | Max Working Insulation Voltage                                                                                                                     | 1,414           | -         | _    | V <sub>peak</sub> |

| VIOTM                 | Highest Allowable Over Voltage                                                                                                                     | 6000            | -         | -    | V <sub>peak</sub> |

|                       | External Creepage                                                                                                                                  | 8               | -         | -    | mm                |

|                       | External Clearance                                                                                                                                 | 7.4             | -         | -    | mm                |

|                       | External Clearance (for Option T or TS – 0.4" Lead Spacing)                                                                                        | 10.16           | -         | -    | mm                |

|                       | Insulation Thickness                                                                                                                               | 0.5             | -         | -    | mm                |

| T <sub>Case</sub>     | Safety Limit Values – Maximum Values Allowed in the Event of a Failure Case Temperature                                                            | 150             | -         | _    | °C                |

| I <sub>S,INPUT</sub>  | Input Current                                                                                                                                      | 25              | -         | _    | mA                |

| P <sub>S,OUTPUT</sub> | Output Power (Duty Factor ≤ 2.7%)                                                                                                                  | 250             | -         | _    | mW                |

| R <sub>IO</sub>       | Insulation Resistance at T <sub>S</sub> , V <sub>IO</sub> = 500 V                                                                                  | 10 <sup>9</sup> | -         | _    | Ω                 |

#### ABSOLUTE MAXIMUM RATINGS (T<sub>A</sub> = 25°C unless otherwise specified)

| Symbol                 | Parameter                                                                            | Value                | Unit |

|------------------------|--------------------------------------------------------------------------------------|----------------------|------|

| T <sub>STG</sub>       | Storage Temperature                                                                  | -40 to +125          | °C   |

| T <sub>OPR</sub>       | Operating Temperature                                                                | -40 to +100          | °C   |

| Τ <sub>J</sub>         | Junction Temperature                                                                 | -40 to +125          | °C   |

| T <sub>SOL</sub>       | Lead Solder Temperature – Wave Solder (Refer to Reflow Temperature Profile, page 15) | 260 for 10 seconds   | °C   |

| I <sub>F(AVG)</sub>    | Average Input Current (Note 1)                                                       | 25                   | mA   |

| I <sub>F(tr, tf)</sub> | LED Current Minimum Rate of Rise/Fall                                                | 250                  | ns   |

| V <sub>R</sub>         | Reverse Input Voltage                                                                | 5                    | V    |

| I <sub>OH(PEAK)</sub>  | "High" Peak Output Current (Note 2)                                                  | 3                    | А    |

| I <sub>OL(PEAK)</sub>  | "Low" Peak Output Current (Note 2)                                                   | 3                    | А    |

| $V_{DD} - V_{SS}$      | Supply Voltage                                                                       | -0.5 to 35           | V    |

| V <sub>O(PEAK)</sub>   | Output Voltage                                                                       | 0 to V <sub>DD</sub> | V    |

| Po                     | Output Power Dissipation (Note 3)                                                    | 250                  | mW   |

| PD                     | Total Power Dissipation (Note 4)                                                     | 295                  | mW   |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

1. Derate linearly above +79°C free air temperature at a rate of 0.37mA/°C.

2. Maximum pulse width = 10  $\mu$ s, maximum duty cycle = 11%.

3. Derate linearly above +79°C, free air temperature at the rate of 5.73 mW/°C.

4. No derating required across operating temperature range.

#### **RECOMMENDED OPERATING CONDITIONS**

| Symbol              | Parameter           | Value       | Unit |

|---------------------|---------------------|-------------|------|

| $V_{DD} - V_{SS}$   | Power Supply        | 10 to 30    | V    |

| I <sub>F(ON)</sub>  | Input Current (ON)  | 10 to 16    | mA   |

| V <sub>F(OFF)</sub> | Input Voltage (OFF) | -3.0 to 0.8 | V    |

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

| Symbol               | Parameter                                  | Test Conditions                                             | Min                   | Тур  | Max                   | Unit  |

|----------------------|--------------------------------------------|-------------------------------------------------------------|-----------------------|------|-----------------------|-------|

| I <sub>OH</sub>      | High Level Output Current                  | V <sub>OH</sub> = (V <sub>DD</sub> - V <sub>SS</sub> - 1 V) | 0.5                   | 0.9  | -                     | А     |

|                      |                                            | $V_{OH} = (V_{DD} - V_{SS} - 6 V)$                          | 2.5                   | _    | -                     |       |

| I <sub>OL</sub>      | Low Level Output Current                   | $V_{OL} = (V_{DD} - V_{SS} + 1 V)$                          | 0.5                   | 1    | -                     | А     |

|                      |                                            | $V_{OL} = (V_{DD} - V_{SS} + 6 V)$                          | 2.5                   | _    | -                     |       |

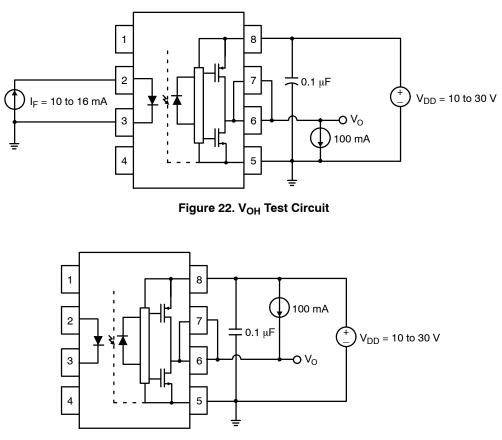

| V <sub>OH</sub>      | High Level Output Voltage (Note 5, 6)      | I <sub>O</sub> = -100 mA                                    | V <sub>DD</sub> – 0.5 | _    | -                     | V     |

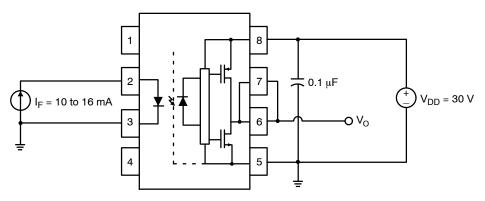

| V <sub>OL</sub>      | Low Level Output Voltage (Note 5, 6)       | I <sub>O</sub> = 100 mA                                     | -                     | _    | V <sub>SS</sub> + 0.5 | V     |

| I <sub>DDH</sub>     | High Level Supply Current                  | Output Open, I <sub>F</sub> = 10 to 16 mA                   | -                     | 2.6  | 4.0                   | mA    |

| I <sub>DDL</sub>     | Low Level Supply Current                   | Output Open, $V_F = -3.0$ to 0.8 V                          | -                     | 2.5  | 4.0                   | mA    |

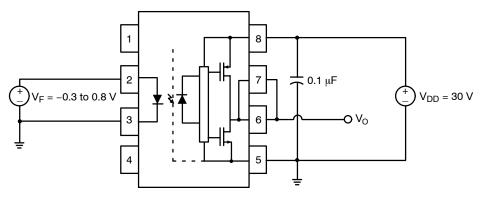

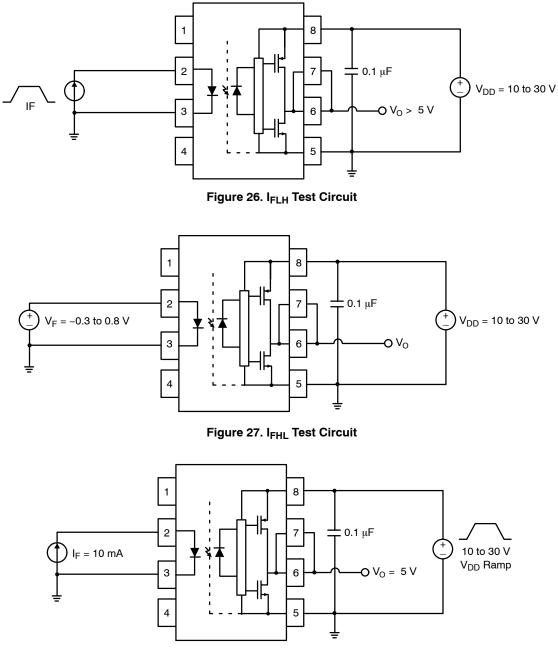

| I <sub>FLH</sub>     | Threshold Input Current Low to High        | I <sub>O</sub> = 0 mA, V <sub>O</sub> > 5 V                 | -                     | 3.0  | 7.5                   | mA    |

| $V_{FHL}$            | Threshold Input Voltage High to Low        | I <sub>O</sub> = 0 mA, V <sub>O</sub> < 5 V                 | 0.8                   | -    | -                     | V     |

| V <sub>F</sub>       | Input Forward Voltage                      | I <sub>F</sub> = 10 mA                                      | 1.1                   | 1.43 | 1.8                   | V     |

| $\Delta V_{F}/T_{A}$ | Temperature Coefficient of Forward Voltage | I <sub>F</sub> = 10 mA                                      | -                     | -1.5 | -                     | mV/°C |

| V <sub>UVLO+</sub>   | UVLO Threshold                             | V <sub>O</sub> > 5V, I <sub>F</sub> = 10 mA                 | 7                     | 8.3  | 9                     | V     |

| V <sub>UVLO</sub> _  |                                            | V <sub>O</sub> < 5V, I <sub>F</sub> = 10 mA                 | 6.5                   | 7.7  | 8.5                   | V     |

| JVLO <sub>HYST</sub> | UVLO Hysteresis                            |                                                             | -                     | 0.6  | -                     | V     |

| BV <sub>R</sub>      | Input Reverse Breakdown Voltage            | I <sub>R</sub> = 10 μA                                      | 5                     | -    | -                     | V     |

| CIN                  | Input Capacitance                          | f = 1 MHz, V <sub>F</sub> = 0 V                             | -                     | 25   | -                     | pF    |

| ELECTRICAL-OPTICAL CHARACTERISTICS (DC) (Apply over all recommended conditions, typical value is measured at |  |

|--------------------------------------------------------------------------------------------------------------|--|

| $V_{DD}$ = 30 V, $V_{SS}$ = 0 V, $T_A$ = 25°C, unless otherwise specified.)                                  |  |

In this test, V<sub>OH</sub> is measured with a dc load current of 100 mA. When driving capacitive load V<sub>OH</sub> will approach V<sub>DD</sub> as I<sub>OH</sub> approaches zero amps.

Maximum pulse width = 1 ms, maximum duty cycle = 20%.

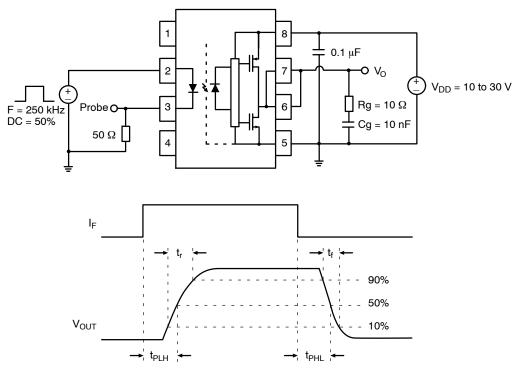

SWITCHING CHARACTERISTICS (Apply over all recommended conditions, typical value is measured at V<sub>DD</sub> = 30 V, V<sub>SS</sub> = 0 V,  $T_A = 25^{\circ}C$ , unless otherwise specified.)

| Symbol                                                    | Parameter                                                         | Test Conditions                                                                                               | Min | Тур | Max | Unit  |

|-----------------------------------------------------------|-------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|-----|-----|-----|-------|

| t <sub>PLH</sub>                                          | Propagation Delay Time to High Output Level (Note 7)              | $I_{\rm F} = 10 \text{ mA}, R_{\rm g} = 10 \Omega,$                                                           | 50  | 120 | 210 | ns    |

| t <sub>PHL</sub>                                          | Propagation Delay Time to Low Output Level (Note 7)               | f = 250 kHz,<br>Duty Cycle = 50%,                                                                             | 50  | 145 | 210 | ns    |

| P <sub>WD</sub>                                           | Pulse Width Distortion (Note 8)                                   | C <sub>g</sub> = 10 nF                                                                                        | -   | 35  | 65  | ns    |

| P <sub>DD</sub><br>(t <sub>PHL</sub> – t <sub>PLH</sub> ) | Propagation Delay Difference Between Any Two Parts (Note 9)       |                                                                                                               | -90 | -   | 90  | ns    |

| t <sub>r</sub>                                            | Rise Time                                                         | $C_L$ = 10 nF, $R_g$ = 10 $\Omega$                                                                            | -   | 38  | -   | ns    |

| t <sub>f</sub>                                            | Fall Time                                                         |                                                                                                               | -   | 24  | -   | ns    |

| t <sub>UVLO ON</sub>                                      | UVLO Turn On Delay                                                |                                                                                                               | -   | 2.0 | -   | μs    |

| t <sub>UVLO</sub> OFF                                     | UVLO Turn Off Delay                                               |                                                                                                               | -   | 0.3 | -   | μs    |

| CM <sub>H</sub>                                           | Output High Level Common Mode Transient Immunity<br>(Note 10, 11) | $ \begin{array}{l} T_{A}=+25^{\circ}C,\ I_{f}=7\ mA\ to\\ 16\ mA,\ V_{CM}=2\ kV,\\ V_{DD}=30\ V \end{array} $ | 35  | 50  | -   | kV/μs |

| CM <sub>L</sub>                                           | Output Low Level Common Mode Transient Immunity (Note 10, 12)     | $ \begin{array}{l} T_{A}=+25^{\circ}C, \ V_{f}=0 \ V, \\ V_{CM}=2 \ kV, \ V_{DD}=30 \ V \end{array} $         | 35  | 50  | -   | kV/μs |

t<sub>PHL</sub> propagation delay is measured from the 50% level on the falling edge of the input pulse to the 50% level of the falling edge of the V<sub>O</sub> 7. signal. t<sub>PLH</sub> propagation delay is measured from the 50% level on the rising edge of the input pulse to the 50% level of the rising edge of the Vo signal.

PWD is defined as | t<sub>PHL</sub> - t<sub>PLH</sub> | for any given device.

The difference between t<sub>PHL</sub> and t<sub>PLH</sub> between any two FOD3182 parts under same operating conditions, with equal loads.

10. Pin 1 and 4 need to be connected to LED common.

11. Common mode transient immunity in the high state is the maximum tolerable dV<sub>CM</sub>/dt of the common mode pulse V<sub>CM</sub> to assure that the output will remain in the high state (i.e.  $V_0 > 15$  V).

12. Common mode transient immunity in a low state is the maximum tolerable dV<sub>CM</sub>/dt of the common mode pulse, V<sub>CM</sub>, to assure that the output will remain in a low state (i.e.  $V_0 < 1.0$  V).

#### INSULATION CHARACTERISTICS

| Symbol           | Parameter                                 | Test Conditions                                                                                                 | Min  | Тур*             | Max | Unit             |

|------------------|-------------------------------------------|-----------------------------------------------------------------------------------------------------------------|------|------------------|-----|------------------|

| V <sub>ISO</sub> | Withstand Isolation Voltage (Note 13, 14) | $\begin{array}{l} T_{A} = 25^{\circ}C, \ R.H. < 50\%, \\ t = 1 \ minute, \ I_{I-O} \leq 10 \ \mu A \end{array}$ | 5000 | -                | -   | V <sub>rms</sub> |

| R <sub>I-O</sub> | Resistance (Input to Output) (Note 14)    | V <sub>I-O</sub> = 500 V                                                                                        | -    | 10 <sup>11</sup> | -   | Ω                |

| C <sub>I-O</sub> | Capacitance (Input to Output)             | Freq. = 1 MHz                                                                                                   | -    | 1                | -   | pF               |

\*Typical values at T<sub>A</sub> = 25°C

13. In accordance with UL 1577, each optocoupler is proof tested by applying an insulation test voltage > 6000 Vrms, 60 Hz for 1 second (leakage detection current limit  $I_{I-O} < 10 \ \mu A$ ).

14. Device considered a two-terminal device: pins on input side shorted together and pins on output side shorted together.

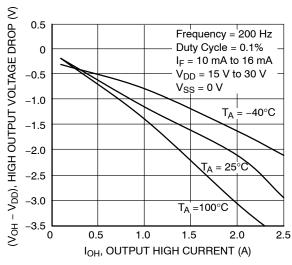

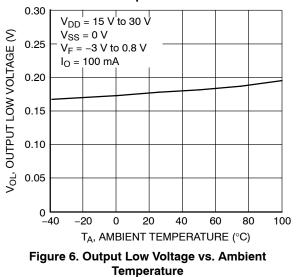

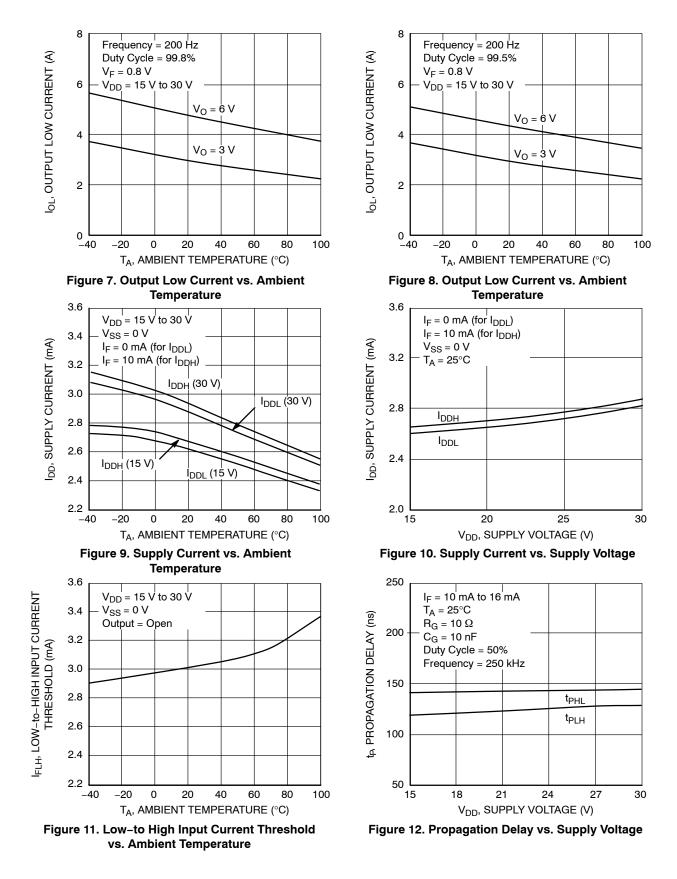

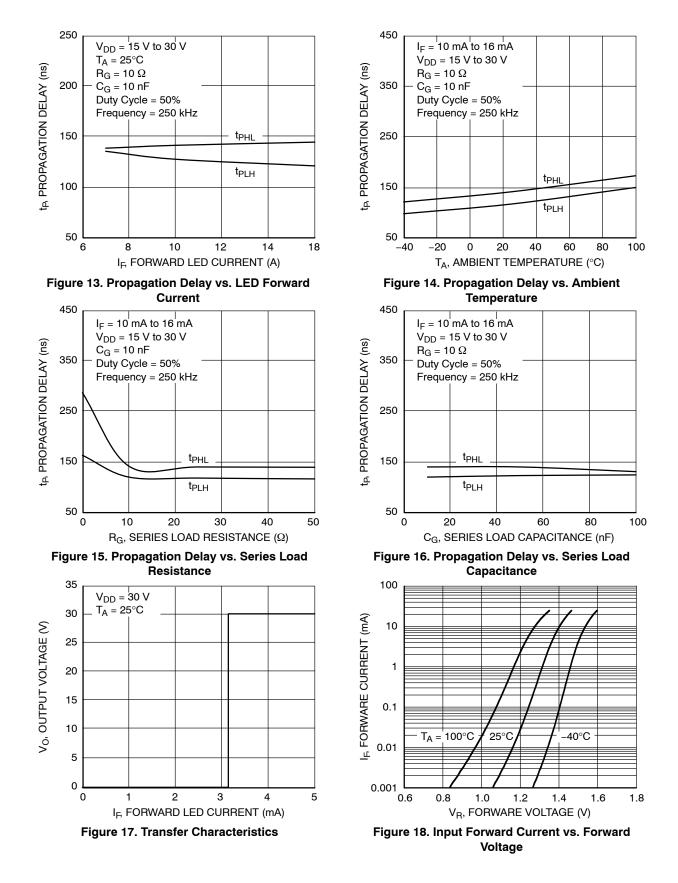

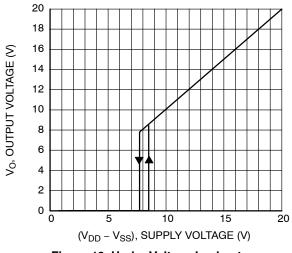

#### **TYPICAL PERFORMANCE CURVES**

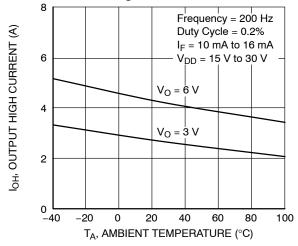

Figure 3. Output High Current vs. Ambient Temperature

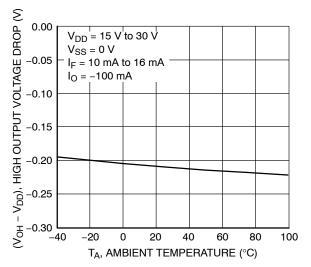

Figure 2. Output High Voltage Drop vs. Ambient Temperature

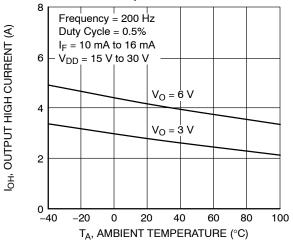

Figure 4. Output High Current vs. Ambient Temperature

www.onsemi.com

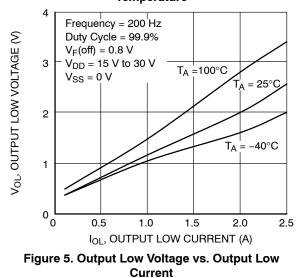

#### TYPICAL PERFORMANCE CURVES (Continued)

#### TYPICAL PERFORMANCE CURVES (Continued)

#### TYPICAL PERFORMANCE CURVES (Continued)

Figure 19. Under Voltage Lockout

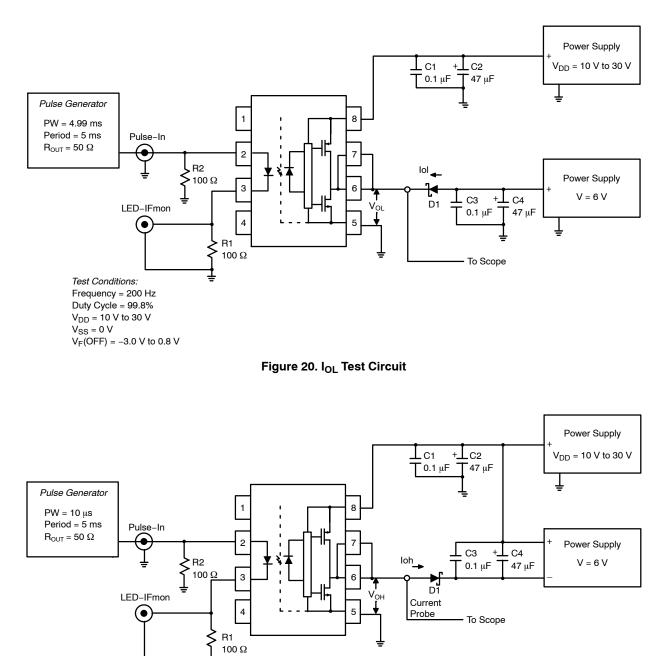

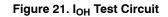

#### **TEST CIRCUIT**

$\label{eq:conditions:} \hline Frequency = 200 \ Hz \\ Duty Cycle = 0.2\% \\ V_{DD} = 10 \ V \ to \ 30 \ V \\ V_{SS} = 0 \ V \\ I_F = 10 \ mA \ to \ 16 \ mA \\ \hline \end{array}$

Figure 23. V<sub>OL</sub> Test Circuit

Figure 24. I<sub>DDH</sub> Test Circuit

Figure 25. I<sub>DDL</sub> Test Circuit

Figure 29.  $t_{PHL}$ ,  $t_{PLH}$ ,  $t_r$  and  $t_f$  Test Circuit and Waveforms

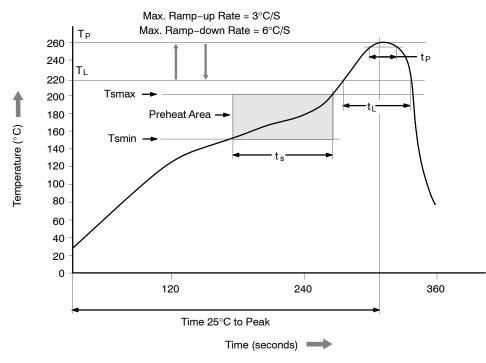

#### **REFLOW PROFILE**

Figure 31. Reflow Profile

#### Table 1.

| Profile Freature                                   | Pb-Free Assembly Profile |

|----------------------------------------------------|--------------------------|

| Temperature Min. (Tsmin)                           | 150°C                    |

| Temperature Max. (Tsmax)                           | 200°C                    |

| Time (t <sub>S</sub> ) from (Tsmin to Tsmax)       | 60–120 seconds           |

| Ramp-up Rate (t <sub>L</sub> to t <sub>P</sub> )   | 3°C/second max.          |

| Liquidous Temperature (TL)                         | 217°C                    |

| Time ( $t_L$ ) Maintained Above ( $T_L$ )          | 60–150 seconds           |

| Peak Body Package Temperature                      | 260°C +0°C / –5°C        |

| Time (t <sub>P</sub> ) within 5°C of 260°C         | 30 seconds               |

| Ramp-down Rate (T <sub>P</sub> to T <sub>L</sub> ) | 6°C/second max.          |

| Time 25°C to Peak Temperature                      | 8 minutes max.           |

#### **ORDERING INFORMATION**

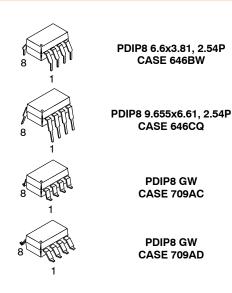

| Part Number                                                                      | Package                                                                            | Shipping <sup>†</sup> |

|----------------------------------------------------------------------------------|------------------------------------------------------------------------------------|-----------------------|

| FOD3182                                                                          | PDIP8 9.655x6.61, 2.54P<br>DIP 8-Pin                                               | 50 Units / Tube       |

| FOD3182S                                                                         | PDIP8 GW<br>SMT 8-Pin (Lead Bend)                                                  | 50 Units / Tube       |

| FOD3182SD                                                                        | PDIP8 GW<br>SMT 8-Pin (Lead Bend)                                                  | 1,000 / Tape and Reel |

| FOD3182V                                                                         | FOD3182V PDIP8 9.655x6.61, 2.54P<br>DIP 8–Pin, IEC60747–5–2 option                 |                       |

| FOD3182SV PDIP8 GW<br>SMT 8-Pin (Lead Bend), DIN EN/IEC 60747-5-2 option         |                                                                                    | 50 Units / Tube       |

| FOD3182SDV                                                                       | PDIP8 GW<br>SMT 8-Pin (Lead Bend), DIN EN/IEC 60747-5-2 option                     | 1,000 / Tape and Reel |

| FOD3182TV                                                                        | PDIP8 6.6x3.81, 2.54P<br>DIP 8–Pin, 0.4" Lead Spacing, DIN EN/IEC 60747–5–2 option | 50 Units / Tube       |

| FOD3182TSV PDIP8 GW<br>SMT 8-Pin, 0.4" Lead Spacing, DIN EN/IEC 60747-5-2 option |                                                                                    | 50 Units / Tube       |

| FOD3182TSR2 PDIP8 GW<br>SMT 8-Pin, 0.4" Lead Spacing                             |                                                                                    | 700 / Tape and Reel   |

| FOD3182TSR2V                                                                     | PDIP8 GW<br>SMT 8-Pin, 0.4" Lead Spacing, DIN EN/IEC 60747-5-2 option              | 700 / Tape and Reel   |

+For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

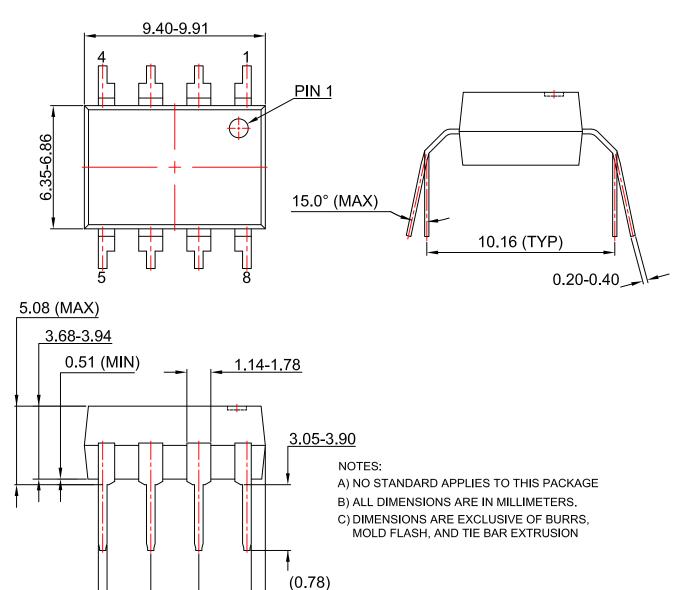

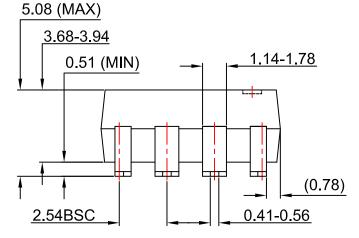

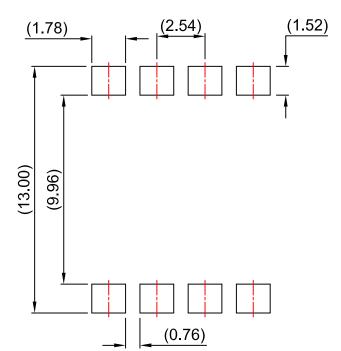

PDIP8 6.6x3.81, 2.54P CASE 646BW ISSUE O

DATE 31 JUL 2016

| DOCUMENT NUMBER: | 98AON13445G Electronic versions are uncontrolled except when accessed directly from the Document Repositor<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |  |             |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|-------------|--|--|

| DESCRIPTION:     | PDIP8 6.6X3.81, 2.54P                                                                                                                                                                         |  | PAGE 1 OF 1 |  |  |

|                  |                                                                                                                                                                                               |  |             |  |  |

2.54 BSC

onsemi and ONSEMi are trademarks of Semiconductor Components Industries, LLC dba onsemi or its subsidiaries in the United States and/or other countries. onsemi reserves the right to make changes without further notice to any products herein. onsemi makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. onsemi does not convey any license under its patent rights nor the rights of others.

0.41-0.56

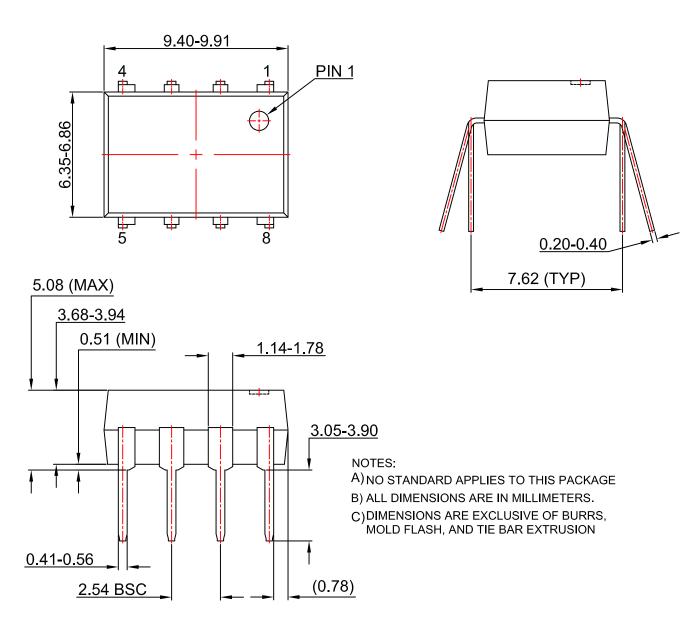

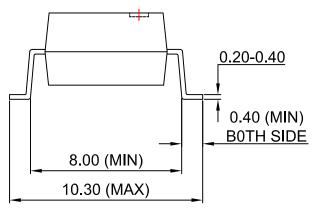

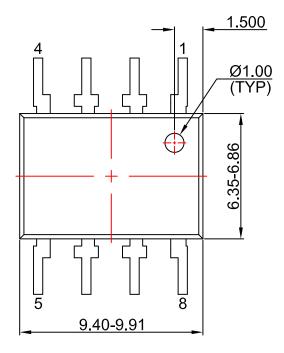

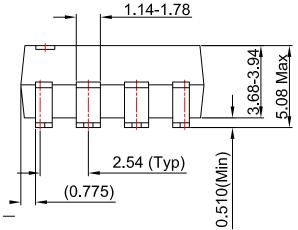

PDIP8 9.655x6.6, 2.54P CASE 646CQ ISSUE O

DATE 18 SEP 2017

| DOCUMENT NUMBER:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 98AON13446G            | Electronic versions are uncontrolled except when accessed directly from the Document Repository.<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|--|

| DESCRIPTION:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | PDIP8 9.655X6.6, 2.54P |                                                                                                                                                                                     | PAGE 1 OF 1 |  |  |

| onsemi and ONSEMi are trademarks of Semiconductor Components Industries, LLC dba onsemi or its subsidiaries in the United States and/or other countries. onsemi reserves the right to make changes without further notice to any products herein. onsemi makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. onsemi does not convey any license under its patent rights nor the rights of others. |                        |                                                                                                                                                                                     |             |  |  |

© Semiconductor Components Industries, LLC, 2017

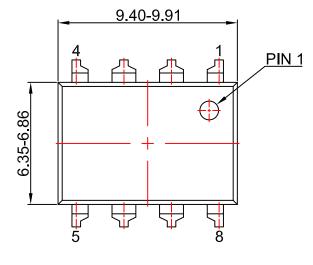

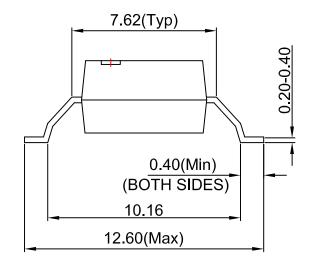

PDIP8 GW CASE 709AC ISSUE O

DATE 31 JUL 2016

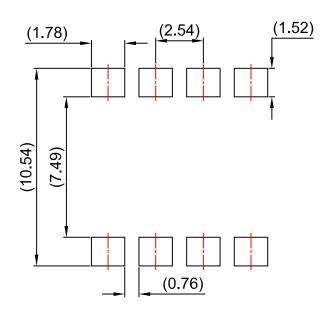

LAND PATTERN RECOMMENDATION

NOTES:

- A) NO STANDARD APPLIES TO THIS PACKAGE

- B) ALL DIMENSIONS ARE IN MILLIMETERS.

- C) DIMENSIONS ARE EXCLUSIVE OF BURRS, MOLD FLASH, AND TIE BAR EXTRUSION

| DOCUMENT NUMBER:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 98AON13447G | Electronic versions are uncontrolled except when accessed directly from the Document Repository.<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|--|

| DESCRIPTION:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | PDIP8 GW    |                                                                                                                                                                                     | PAGE 1 OF 1 |  |  |

| onsemi and ONSEMI, are trademarks of Semiconductor Components Industries, LLC dba onsemi or its subsidiaries in the United States and/or other countries. onsemi reserves the right to make changes without further notice to any products herein. onsemi makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. onsemi does not convey any license under its patent rights nor the rights of others. |             |                                                                                                                                                                                     |             |  |  |

PDIP8 GW CASE 709AD ISSUE O

DATE 31 JUL 2016

LAND PATTERN RECOMMENDATION

#### NOTES:

- A) NO STANDARD APPLIES TO THIS PACKAGE

- B) ALL DIMENSIONS ARE IN MILLIMETERS.

- C) DIMENSIONS ARE EXCLUSIVE OF BURRS, MOLD FLASH, AND TIE BAR EXTRUSION

| DOCUMENT NUMBER: | 98AON13448G | Electronic versions are uncontrolled except when accessed directly from the Document Repository.<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |

|------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| DESCRIPTION:     | PDIP8 GW    |                                                                                                                                                                                     | PAGE 1 OF 1 |

onsemi and ONSEMi are trademarks of Semiconductor Components Industries, LLC dba onsemi or its subsidiaries in the United States and/or other countries. onsemi reserves the right to make changes without further notice to any products herein. onsemi makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. onsemi does not convey any license under its patent rights of others.

onsemi, ONSEMI, and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <u>www.onsemi.com/site/pdf/Patent\_Marking.pdf</u>. onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or indental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi does not convey any license under any of its intellectual property rights nor the rights of others. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification. Buyer shall indemnify and hold onsemi and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs,

#### ADDITIONAL INFORMATION

TECHNICAL PUBLICATIONS:

Technical Library: www.onsemi.com/design/resources/technical-documentation onsemi Website: www.onsemi.com

ONLINE SUPPORT: <u>www.onsemi.com/support</u> For additional information, please contact your local Sales Representative at <u>www.onsemi.com/support/sales</u>