# LDO Regulator - 1 A, Ultra Low Dropout, CMOS, with Bias Rail

Product Preview

# T30LMPSR131, T30LAPSR131

The T30LxPSR131 is a 1 A LDO equipped with an NMOS pass transistor and a separate bias supply voltage ( $V_{BIAS}$ ). The T30LxPSR131 offers ultra-fast dynamic response and provides very stable output voltage with 1% accuracy over full temperature range. To optimize performance for battery operated portable applications, the T30LxPSR131 features an ultra-low bias current consumption. The device also features high PSRR across frequency range and ultra-low noise optimized for noise sensitive applications. The WLCSP6 1.145 mm x 0.75 mm, 0.4 mm pitch Chip Scale package is optimized for use in space constrained applications.

### **Features**

- Best-in-Class Dropout: 25 mV (typ.) at 1 A

- ±1% Accuracy over -40 °C to 125 °C Temperature Range

- Ultra Low Bias Input Current of Typ. 85 μA

- Low Noise, 7.5 μV<sub>RMS</sub> Typ.

- High PSRR across Frequency Range

- ◆ 75 dB at 1 kHz

- ◆ 34 dB at 100 kHz

- Input Voltage Range: up to 2.2 V

- Bias Voltage Range: up to 3.3 V

- Output Voltage Range: 0.5 V to 1.8 V (Fixed), Resolution 25 mV

- Excellent Load Transient Performance

- 1.2 V Logic Level Enable Input Compatibility

- Normal and Slow Turn-On Options Available

- Output Active Discharge Option Available

# **Typical Applications**

- Battery-powered Equipment

- Smartphones, Tablets

- Cameras, DVRs, STB and Camcorders

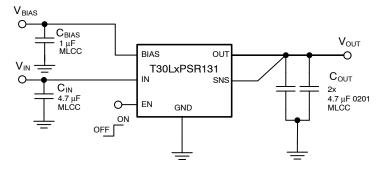

Figure 1. Application Schematic

WLCSP6 1.145x0.75x0.33 CASE 567YX

## MARKING DIAGRAM

XX = Specific Device Code M = Month Code

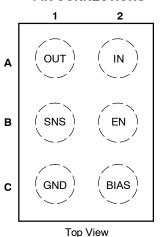

### **PIN CONNECTIONS**

## ORDERING INFORMATION

See detailed ordering and shipping information on page 4 of this data sheet.

This document contains information on a product under development. **onsemi** reserves the right to change or discontinue this product without notice.

# T30LMPSR131, T30LAPSR131

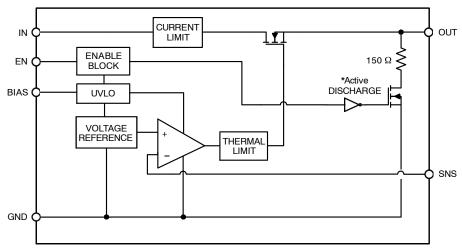

\*Active output discharge function is present only in "A" and "C" option devices.

Figure 2. Simplified Schematic Block Diagram - Fixed Version

#### PIN FUNCTION DESCRIPTION

| Pin No.<br>WLCSP6 | Pin Name | Description                                                                                                          |

|-------------------|----------|----------------------------------------------------------------------------------------------------------------------|

| A1                | OUT      | Regulated Output Voltage pin                                                                                         |

| A2                | IN       | Input Voltage Supply pin                                                                                             |

| B1                | SNS      | Output voltage Sensing Input. Connect to Output on the PCB to output the voltage corresponding to the part version.  |

| B2                | EN       | Enable pin. Driving this pin high enables the regulator. Driving this pin low puts the regulator into shutdown mode. |

| C1                | GND      | Ground pin                                                                                                           |

| C2                | BIAS     | Bias voltage supply for internal control circuits.                                                                   |

# **ABSOLUTE MAXIMUM RATINGS**

| Rating                                        | Symbol                                                 | Value                              | Unit |

|-----------------------------------------------|--------------------------------------------------------|------------------------------------|------|

| Input Voltage (Note 1)                        | V <sub>IN</sub>                                        | -0.3 to 2.5                        | V    |

| Output Voltage                                | V <sub>OUT</sub>                                       | $-0.3$ to $(V_{IN} + 0.3) \le 2.5$ | V    |

| Chip Enable, Bias and SNS Input               | V <sub>EN</sub> , V <sub>BIAS</sub> , V <sub>SNS</sub> | -0.3 to 3.6                        | V    |

| Output Short Circuit Duration                 | t <sub>SC</sub>                                        | unlimited                          | s    |

| Maximum Junction Temperature                  | T <sub>J</sub>                                         | 150                                | °C   |

| Storage Temperature                           | T <sub>STG</sub>                                       | -55 to 150                         | °C   |

| ESD Capability, Human Body Model (Note 2)     | ESD <sub>HBM</sub>                                     | 2000                               | V    |

| ESD Capability, Charged Device Model (Note 2) | ESD <sub>CDM</sub>                                     | 750                                | V    |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

- 1. Refer to ELECTRICAL CHĂRACTERISTICS and APPLICATION INFORMATION for Safe Operating Area.

- 2. This device series incorporates ESD protection (except OUT pin) and is tested by the following methods:

- ESD Human Body Model tested per EIA/JESD22-A114

- ESD Charged Device Model tested per JS-002-2018

- Latchup Current Maximum Rating tested per JEDEC standard: JESD78

# THERMAL CHARACTERISTICS

| Rating                                                                                          | Symbol         | Value | Unit |

|-------------------------------------------------------------------------------------------------|----------------|-------|------|

| Thermal Characteristics, WLCSP6 1.145 mm x 0.75 mm Thermal Resistance, Junction-to-Air (Note 3) | $R_{\thetaJA}$ | 69    | °C/W |

<sup>3.</sup> This junction-to-ambient thermal resistance under natural convection was derived by thermal simulations based on the JEDEC JESD51 series standards methodology. Only a single device mounted at the center of a high\_K (2s2p) 80 mm x 80 mm multilayer board with 1-ounce internal planes and 2-ounce copper on top and bottom. Top copper layer has a dedicated 1.6 mm2 copper area.

# T30LMPSR131, T30LAPSR131

# **ELECTRICAL CHARACTERISTICS**

$(-40 \text{ °C} \le T_J \le 125 \text{ °C}; V_{BIAS} = 2.7 \text{ V or } (V_{OUT} + 1.6 \text{ V}), \text{ whichever is greater, } V_{IN} = V_{OUT(NOM)} + 0.1 \text{ V}, I_{OUT} = 1 \text{ mA, } V_{EN} = 1 \text{ V}, C_{IN} = 4.7 \text{ μF, } C_{OUT} = 10 \text{ μF, } C_{BIAS} = 1 \text{ μF, unless otherwise noted.}$  Typical values are at  $T_J = +25 \text{ °C}$ . Min/Max values are for  $-40 \text{ °C} \le T_J \le 125 \text{ °C}$  unless otherwise noted. (Note 4))

| Parameter                         | Test Condition                                                                                                                                                                                                                                                                                                  | Symbol                 | Min                             | Тур                           | Max   | Unit |               |

|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|---------------------------------|-------------------------------|-------|------|---------------|

| Operating Input Voltage<br>Range  |                                                                                                                                                                                                                                                                                                                 | V <sub>IN</sub>        | $V_{OUT} + V_{DO}$              |                               | 2.2   | V    |               |

| Operating Bias Voltage<br>Range   |                                                                                                                                                                                                                                                                                                                 | V <sub>BIAS</sub>      | (V <sub>OUT</sub> + 1.50) ≥ 2.5 |                               | 3.3   | V    |               |

| Undervoltage Lock-out             | V <sub>BIAS</sub> Rising<br>Hysteresis                                                                                                                                                                                                                                                                          | UVLO <sub>(BIAS)</sub> |                                 | 2.1<br>0.1                    |       | V    |               |

|                                   | V <sub>IN</sub> Rising<br>Hysteresis                                                                                                                                                                                                                                                                            | UVLO <sub>(IN)</sub>   |                                 | 0.8 x V <sub>OUT</sub><br>0.1 |       | V    |               |

| Output Voltage Accuracy           | $\begin{array}{l} -40~^{\circ}\text{C} \leq T_{J} \leq 85~^{\circ}\text{C}, \\ V_{OUT(NOM)} + 0.1~\text{V} \leq \text{V}_{IN} \leq \\ +~1.0~\text{V},~2.7~\text{V}~\text{or}~\text{(V}_{OUT(NC)} \\ \text{whichever is greater} < V_{BI} \\ 1~\text{mA} < I_{OUT} < 1~\text{A} \end{array}$                     | V <sub>OUT</sub>       | -0.8                            |                               | +0.8  | %    |               |

| Output Voltage Accuracy           | $\begin{array}{l} -40~^{\circ}\text{C} \leq T_{J} \leq 125~^{\circ}\text{C},\\ \text{V}_{OUT(NOM)} + 0.1~\text{V} \leq \text{V}_{IN} \leq \\ +~1.0~\text{V},~2.7~\text{V}~\text{or}~(\text{V}_{OUT(NC)})\\ \text{whichever is greater} < \text{V}_{BI}\\ 1~\text{mA} < \text{I}_{OUT} < 1~\text{A} \end{array}$ |                        | -1.0                            |                               | +1.0  | %    |               |

| V <sub>IN</sub> Line Regulation   | $V_{OUT(NOM)} + 0.1 V \le V_{IN} \le$                                                                                                                                                                                                                                                                           | Line <sub>Reg</sub>    |                                 | 0.01                          |       | %/V  |               |

| V <sub>BIAS</sub> Line Regulation | 2.7 V or (V <sub>OUT(NOM)</sub> + 1.6<br>whichever is greater < V <sub>BI</sub>                                                                                                                                                                                                                                 | Line <sub>Reg</sub>    |                                 | 0.01                          |       | %/V  |               |

| Load Regulation                   | I <sub>OUT</sub> = 1 mA to 1 A                                                                                                                                                                                                                                                                                  | Load <sub>Reg</sub>    |                                 | 1                             |       | mV   |               |

| V <sub>IN</sub> Dropout Voltage   | I <sub>OUT</sub> = 1 A (Note 5)                                                                                                                                                                                                                                                                                 | $V_{DO}$               |                                 | 25                            | 60    | mV   |               |

| V <sub>BIAS</sub> Dropout Voltage | I <sub>OUT</sub> = 1 A,<br>V <sub>IN</sub> = V <sub>BIAS</sub> (Notes 5, 6)                                                                                                                                                                                                                                     | V <sub>DO</sub>        |                                 | 1.1                           | 1.5   | V    |               |

| Output Current Limit              | V <sub>OUT</sub> = 90% V <sub>OUT(NOM)</sub>                                                                                                                                                                                                                                                                    | I <sub>CL</sub>        | 1250                            | 1650                          | 2000  | mA   |               |

| SNS Pin Operating Current         |                                                                                                                                                                                                                                                                                                                 | I <sub>SNS</sub>       |                                 | 0.1                           | 0.5   | μΑ   |               |

| Bias Pin Quiescent Current        | V <sub>BIAS</sub> = 3.3 V, I <sub>OUT</sub> = 0 mA                                                                                                                                                                                                                                                              |                        | I <sub>BIASQ</sub>              |                               | 85    | 130  | μΑ            |

| Bias Pin Disable Current          | V <sub>EN</sub> ≤ 0.325 V                                                                                                                                                                                                                                                                                       |                        |                                 |                               | 0.5   | TBD  | μΑ            |

| Input Pin Disable Current         | -                                                                                                                                                                                                                                                                                                               |                        |                                 |                               | 0.5   | TBD  | μΑ            |

| EN Pin Threshold Voltage          | EN Input Voltage "H"                                                                                                                                                                                                                                                                                            |                        | V <sub>EN(H)</sub>              | 0.825                         |       |      | V             |

|                                   | EN Input Voltage "L"                                                                                                                                                                                                                                                                                            | V <sub>EN(L)</sub>     |                                 |                               | 0.325 |      |               |

| EN Pull Down Current              | V <sub>EN</sub> = 3.3 V                                                                                                                                                                                                                                                                                         |                        | I <sub>EN</sub>                 |                               | 0.3   | TBD  | μΑ            |

| Power Supply Rejection            | V <sub>IN</sub> to V <sub>OUT</sub> ,                                                                                                                                                                                                                                                                           | f = 100 Hz             | PSRR(V <sub>IN</sub> )          |                               | 73    |      | dB            |

| Ratio                             | $V_{IN} = V_{OUT} + 0.1 \text{ V},$ $I_{OUT} = 450 \text{ mA},$ $C_{OUT} = 2 \text{ x } 4.7  \mu\text{F } 0201$                                                                                                                                                                                                 | f = 1 kHz              |                                 |                               | 73    |      | 1             |

|                                   |                                                                                                                                                                                                                                                                                                                 | f = 10 kHz             |                                 |                               | 50    |      | 1             |

|                                   |                                                                                                                                                                                                                                                                                                                 | f = 100 kHz            |                                 |                               | 33    |      | 1             |

|                                   | V <sub>BIAS</sub> to V <sub>OUT</sub> ,<br>V <sub>IN</sub> = V <sub>OUT</sub> + 0.1 V                                                                                                                                                                                                                           | f = 1 kHz              | PSRR(V <sub>BIAS</sub> )        |                               | 80    |      | dB            |

| Output Noise Voltage              | Voltage $V_{IN} = V_{OUT} + 0.1 V$ ,                                                                                                                                                                                                                                                                            |                        | V <sub>N</sub>                  |                               | 10    |      | $\mu V_{RMS}$ |

|                                   | f = 10 Hz to 100 kHz                                                                                                                                                                                                                                                                                            | I <sub>OUT</sub> = 1 A | 1                               |                               | 7.5   |      | 1             |

| Thermal Shutdown                  | Temperature increasing                                                                                                                                                                                                                                                                                          |                        |                                 | 160                           |       | °C   |               |

| Threshold                         | Temperature decreasing                                                                                                                                                                                                                                                                                          |                        |                                 | 140                           |       | 1    |               |

# T30LMPSR131, T30LAPSR131

# **ELECTRICAL CHARACTERISTICS** (continued)

$(-40~{}^{\circ}\text{C} \le T_{J} \le 125~{}^{\circ}\text{C}; V_{BIAS} = 2.7~V \text{ or } (V_{OUT} + 1.6~V), \text{ whichever is greater, } V_{IN} = V_{OUT(NOM)} + 0.1~V, I_{OUT} = 1~\text{mA}, V_{EN} = 1~V, C_{IN} = 4.7~\mu\text{F}, C_{OUT} = 10~\mu\text{F}, C_{BIAS} = 1~\mu\text{F}, \text{ unless otherwise noted.}$

Typical values are at  $T_J = +25$  °C. Min/Max values are for -40 °C  $\leq T_J \leq 125$  °C unless otherwise noted. (Note 4))

| Parameter                     | Test Conditio                                | Test Conditions                                                                       |                    | Min | Тур | Max | Unit |

|-------------------------------|----------------------------------------------|---------------------------------------------------------------------------------------|--------------------|-----|-----|-----|------|

| Output Discharge<br>Pull-Down |                                              | V <sub>EN</sub> ≤ 0.325 V, V <sub>OUT</sub> = 0.5 V,<br>Active Discharge Version Only |                    |     | 150 |     | Ω    |

| Delay time                    | From assertion of V <sub>EN</sub> to         | "A" option                                                                            | t <sub>DELAY</sub> |     | 120 |     | μs   |

|                               | output voltage increase                      | "C" option                                                                            | 1                  |     | 120 |     |      |

| Rise time                     | V <sub>OUT</sub> rise from 10% to            | "A" option                                                                            | t <sub>RISE</sub>  |     | 21  |     |      |

|                               | 90% V <sub>OUT(NOM)</sub>                    | "C" option                                                                            | 1                  |     | 100 |     |      |

| Turn-On Time                  | From assertion of V <sub>EN</sub> to         | "A" option                                                                            | t <sub>ON</sub>    |     | 140 |     |      |

|                               | V <sub>OUT</sub> = 98% V <sub>OUT(NOM)</sub> | "C" option                                                                            | 1                  |     | 220 |     | 1    |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

- Performance guaranteed over the indicated operating temperature range by design and/or characterization. Production tested at T<sub>A</sub> = 25 °C. Low duty cycle pulse techniques are used during the testing to maintain the junction temperature as close to ambient as possible.

- 5. Dropout voltage is characterized when  $V_{OUT}$  falls 3% below  $V_{OUT(NOM)}$ .

- 6. For fixed output voltages below 1.5 V, V<sub>BIAS</sub> dropout does not apply due to a minimum Bias operating voltage of 2.5 V.

## **ORDERING INFORMATION**

| Device      | Nominal<br>Output<br>Voltage | Marking | Option | Package                                                  | Shipping <sup>†</sup> |

|-------------|------------------------------|---------|--------|----------------------------------------------------------|-----------------------|

| T30LMPSR131 | TBD V                        | TBD     | TBD    | WLCSP6<br>Case 567YX<br>(Pb-Free)                        | 10,000 / Tape & Reel  |

| T30LAPSR131 | TBD V                        | TBD     |        | UBM: 240 μm<br>Bump Type:<br>(98.2% Sn/1.8% Ag)<br>Plate |                       |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, <a href="https://example.com/BRD8011/D">BRD8011/D</a>.

<sup>7.</sup> To order other package and voltage variants, please contact your **onsemi** sales representative.

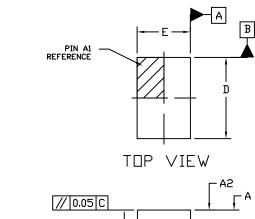

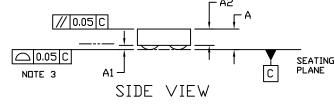

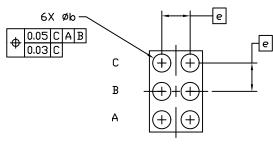

# WLCSP6 1.145x0.75x0.33

CASE 567YX ISSUE O

**DATE 29 JAN 2020**

ı 2 B□TT□M VIEW

# GENERIC MARKING DIAGRAM\*

• XXM

XX = Specific Device Code M = Month Code

\*This information is generic. Please refer to device data sheet for actual part marking. Pb-Free indicator, "G" or microdot "•", may or may not be present. Some products may not follow the Generic Marking.

#### NOTES:

- DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994.

- 2. CONTROLLING DIMENSION: MILLIMETERS

- COPLANARITY APPLIES TO THE SPHERICAL CROWNS OF THE SOLDER BALLS.

- DATUM C, THE SEATING PLANE, IS DEFINED BY THE SPHERICAL CROWNS OF THE SOLDER BALLS.

- 5. DIMENSION 6 IS MEASURED AT THE MAXIMUM SOLDER BALL DIAMETER PARALLEL TO DATUM C.

|     | MILLIMETERS    |       |       |  |  |  |

|-----|----------------|-------|-------|--|--|--|

| DIM | MIN. N□M. MAX. |       |       |  |  |  |

| Α   |                |       | 0.33  |  |  |  |

| A1  | 0.04           | 0.06  | 0.08  |  |  |  |

| A2  | 0.230 REF      |       |       |  |  |  |

| b   | 0.220          | 0.240 | 0.260 |  |  |  |

| D   | 1.095          | 1.145 | 1.195 |  |  |  |

| E   | 0.700          | 0.750 | 0.800 |  |  |  |

| е   | 0.400 BSC      |       |       |  |  |  |

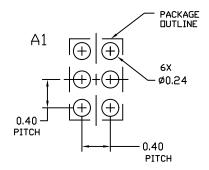

# RECOMMENDED MOUNTING FOOTPRINT

\* For additional information on our Pb-Free strategy and soldering details, please download the DN Semiconductor Soldering and Mounting Techniques Reference Manual, SDLDERRM/D.

| DOCUMENT NUMBER: | 98AON17297H            | Electronic versions are uncontrolled except when accessed directly from the Document Report Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |  |  |

|------------------|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|--|--|

| DESCRIPTION:     | WLCSP6 1.145x0.75x0.33 |                                                                                                                                                                             | PAGE 1 OF 1 |  |  |  |

onsemi and ONSEMI are trademarks of Semiconductor Components Industries, LLC dba onsemi or its subsidiaries in the United States and/or other countries. onsemi reserves the right to make changes without further notice to any products herein. onsemi makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. onsemi does not convey any license under its patent rights nor the rights of others.

onsemi, Onsemi, and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. Onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi does not convey any license under any of its intellectual property rights nor the rights of others. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA class 3 medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase

#### ADDITIONAL INFORMATION

**TECHNICAL PUBLICATIONS:**

$\textbf{Technical Library:} \ \underline{www.onsemi.com/design/resources/technical-documentation}$

onsemi Website: www.onsemi.com

ONLINE SUPPORT: www.onsemi.com/support

For additional information, please contact your local Sales Representative at

www.onsemi.com/support/sales