# **Automotive Power Over Coax Power Management IC for Safety Camera**

# NCV92310

The NCV92310 is part of the onsemi image sensor power management IC (PMIC) family. It is optimized to supply power over coax (POC) automotive application sub-systems such as rear, front and surround view cameras. This NCV92310 integrates one power over coax DCDC converter, 2 high efficiency (1 A and 500 mA) Step-down DCDC converters with DVS (Dynamic Voltage Scale) and 1 low dropout (LDO) voltage regulators in a 3.5x3.5 mm QFNW20 package.

## Features

- 1 Power Over Coax DCDC Converter (2.15 MHz, 2.2 µH/10 µF, 1.2 A)

- Programmable Output Voltage from 2.8 V to 5.0 V by 100 mV Steps

- 1 DCDC Converters (2.15 MHz, 1  $\mu$ H/10  $\mu$ F, 1 A)

- Programmable Output Voltage from 0.6 V to 2.175 V by 25 mV Steps

- 1 DCDC Converters (2.15 MHz, 1 µH/10 µF, 500 mA)

- Programmable Output Voltage from 0.6 V to 2.175 V by 25 mV Steps

- 1 Low Noise Low Drop Out Regulator (2.2 μF, 300 mA)

- Programmable Output Voltage from 2.6 V to 3.3 V by 100 mV Steps

- ◆ 50 µVrms Typical Low Output Noise (Vout = 2.8 V, 10 Hz to 100 kHz)

- Control

- ♦ 400 kHz / 1 MHz I<sup>2</sup>C Compatible

- I<sup>2</sup>C Enable Control Bits

- ◆ /RST and Interrupt Output Pin

- Customizable Power Up / Down Sequence with Soft Start

- Extended Input Voltage Range from 4.6 V to 18 V

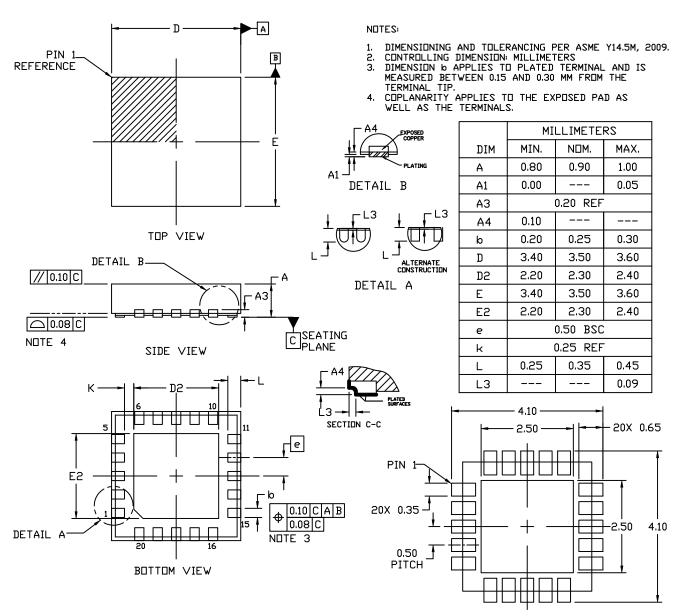

- Footprint: 3.5x3.5 mm QFNW-20 0.5 mm Pitch

## Applications

- Power Over Coax POL Supply

- Automotive ADAS Camera Modules

- Industrial Camera Modules

QFNW20 3.5x3.5, 0.5P CASE 484AV

## MARKING DIAGRAM

Α

Y

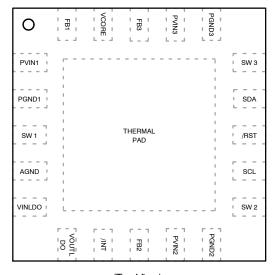

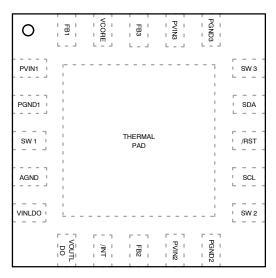

## **PIN CONNECTIONS**

(Top View) 20-Pins 3.5x3.5 0.50 mm pitch DFN

## **ORDERING INFORMATION**

See detailed ordering and shipping information on page 59 of this data sheet.

# TABLE OF CONTENTS

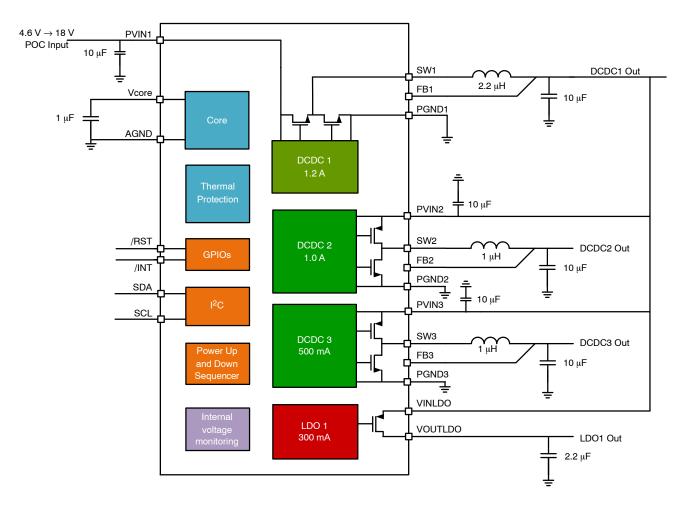

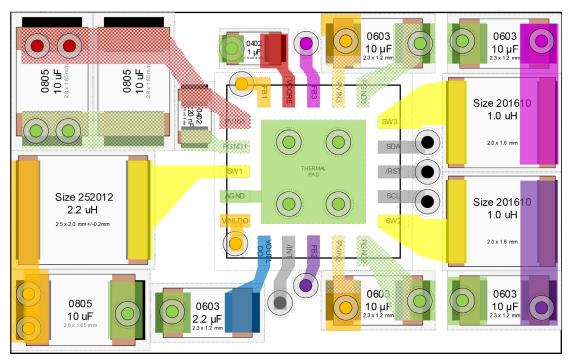

Figure 1. Typical Application Circuit

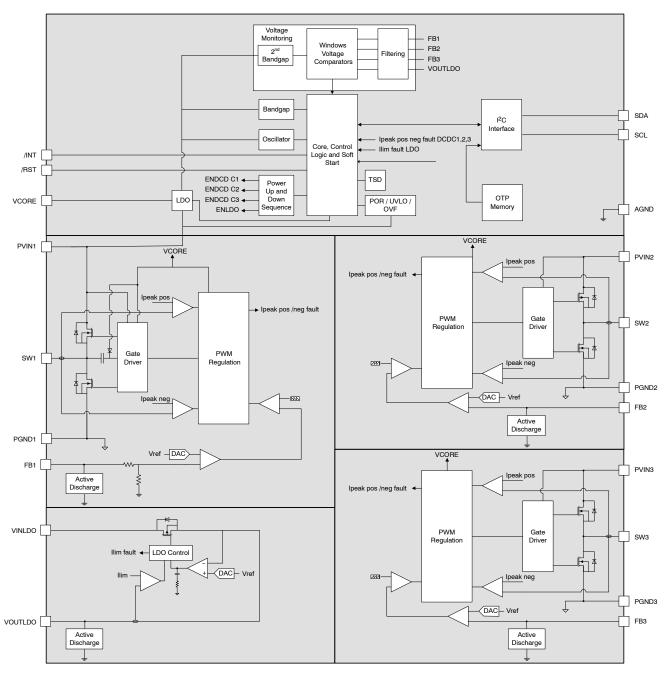

# FUNCTIONAL BLOCK DIAGRAM

Figure 2. Simplified Block Diagram

# **PIN OUT DESCRIPTION**

Figure 3. Pin Out (Top view)

## **PIN FUNCTION DESCRIPTION**

| Pin   | Name        | Туре           | Description                                                                                                                                                                                                                                                  |  |  |  |

|-------|-------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| GENE  | ERAL        | •              |                                                                                                                                                                                                                                                              |  |  |  |

| 19    | VCORE       | Analog Output  | Reference voltage. A 1 $\mu$ F ceramic capacitor (220 nF minimum) must bypass this pin to ground.                                                                                                                                                            |  |  |  |

| 4     | AGND        | Analog Ground  | Analog Ground. Analog and digital modules ground. Must be connected to the system ground.                                                                                                                                                                    |  |  |  |

| 7     | /INT        | Digital Output | errupt push-pull output.                                                                                                                                                                                                                                     |  |  |  |

| 13    | /RST        | Digital Output | Reset push-pull output.                                                                                                                                                                                                                                      |  |  |  |

| 12    | SCL         | Digital Input  | I <sup>2</sup> C interface Clock                                                                                                                                                                                                                             |  |  |  |

| 14    | SDA         | Digital Input  | I <sup>2</sup> C interface Data                                                                                                                                                                                                                              |  |  |  |

| 21    | PAD         | Exposed Pad    | Exposed Pad. Must be soldered to system ground to achieve power dissipation performances.<br>This pin is internally unconnected.                                                                                                                             |  |  |  |

| PoC I | DC-DC CONVE | RTERS          |                                                                                                                                                                                                                                                              |  |  |  |

| 1     | PVIN1       | Power Input    | DCDC1 and Core Power Supply. This pin must be decoupled to ground by a 10 $\mu F$ ceramic capacitor. This capacitor should be placed as close as possible to this pin.                                                                                       |  |  |  |

| 3     | SW1         | Power Output   | DCDC1 Switch Power. This pin connects the power transistors to one end of the inductor. Typical application uses 2.2 $\mu$ H inductor; refer to <u>Application</u> section for more information.                                                             |  |  |  |

| 20    | FB1         | Analog Input   | DCDC1 Feedback Voltage. This pin is the input to the error amplifier and must be connected to the output capacitor.                                                                                                                                          |  |  |  |

| 2     | PGND1       | Power Ground   | DCDC Power Ground. This pin is the power ground and carries the high switching current.<br>A high quality ground must be provided to prevent noise spikes. A local ground plane is<br>recommended to avoid high-density current flow in a limited PCB track. |  |  |  |

| 1 A L | OW VOLTAGE  | DC-DC CONVER   | TERS                                                                                                                                                                                                                                                         |  |  |  |

| 9     | PVIN2       | Power Input    | DCDC2 Power Supply. This pin must be decoupled to ground by a 10 $\mu F$ ceramic capacitor. This capacitor should be placed as close as possible to this pin.                                                                                                |  |  |  |

| 11    | SW2         | Power Output   | DCDC2 Switch Power. This pin connects the power transistors to one end of the inductor. Typical application uses 1.0 $\mu$ H inductor; refer to <u>Application</u> section for more information.                                                             |  |  |  |

| 8     | FB2         | Analog Input   | DCDC2 Feedback Voltage. This pin is the input to the error amplifier and must be connected to                                                                                                                                                                |  |  |  |

the output capacitor.

#### **PIN FUNCTION DESCRIPTION** (continued)

| Pin   | Name                                                                                                                                                                                                                                                                                                | Туре         | Description                                                                                                                                                                                                                                                   |  |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1 A L | OW VOLTAGE I                                                                                                                                                                                                                                                                                        | DC-DC CONVER | TERS                                                                                                                                                                                                                                                          |  |

| 10    | PGND2         Power Ground         DCDC2 Power Ground. This pin is the power ground and carries the high switching current           A high quality ground must be provided to prevent noise spikes. A local ground plane is recommended to avoid high-density current flow in a limited PCB track. |              |                                                                                                                                                                                                                                                               |  |

| 500 m | A LOW VOLTA                                                                                                                                                                                                                                                                                         | GE DC-DC CON | VERTERS                                                                                                                                                                                                                                                       |  |

| 17    | PVIN3                                                                                                                                                                                                                                                                                               | Power Input  | DCDC3 Power Supply. This pin must be decoupled to ground by a 10 $\mu F$ ceramic capacitor. This capacitor should be placed as close as possible to this pin.                                                                                                 |  |

| 15    | SW3                                                                                                                                                                                                                                                                                                 | Power Output | DCDC3 Switch Power. This pin connects the power transistors to one end of the inductor. Typical application uses 1.0 $\mu$ H inductor; refer to <u>Application</u> section for more information.                                                              |  |

| 18    | FB3                                                                                                                                                                                                                                                                                                 | Analog Input | DCDC3 Feedback Voltage. This pin is the input to the error amplifier and must be connected to the output capacitor.                                                                                                                                           |  |

| 16    | PGND3                                                                                                                                                                                                                                                                                               | Power Ground | DCDC3 Power Ground. This pin is the power ground and carries the high switching current.<br>A high quality ground must be provided to prevent noise spikes. A local ground plane is<br>recommended to avoid high-density current flow in a limited PCB track. |  |

| LDO   | REGULATORS                                                                                                                                                                                                                                                                                          | •            | •                                                                                                                                                                                                                                                             |  |

| 5     | VINLDO                                                                                                                                                                                                                                                                                              | Power Input  | LDO Power Supply                                                                                                                                                                                                                                              |  |

| 6     | VOUTLDO                                                                                                                                                                                                                                                                                             | Power Output | LDO Output Power. This pin requires a 2.2 $\mu$ F decoupling capacitor.                                                                                                                                                                                       |  |

#### MAXIMUM RATINGS

| Symbol            | Parameter                                                                     | Min  | Тур    | Max                | Unit |

|-------------------|-------------------------------------------------------------------------------|------|--------|--------------------|------|

| VP1-DC            | Power Pins DC Non Switching: PVIN1, SW1 (Note 1)                              | -0.3 | -      | 20                 | V    |

| VP2-DC            | Power Pins DC Non Switching: PVIN2, PVIN3, SW2, SW3 (Note 1)                  | -0.3 | -      | 6.0                | V    |

| VA1-DC            | Analog Pins DC Non Switching: FB2, FB3 (Note 1)                               | -0.3 | -      | V <sub>CORE</sub>  | V    |

| VA2-DC            | Analog Pins DC Non Switching: VCORE, FB1, VINLDO, VOUTLDO (Note 1)            | -0.3 | -      | 6.0                | V    |

| VA3-DC            | Analog Pins DC Non Switching: VOUTLDO (Note 1)                                | -0.3 | -      | V <sub>INLDO</sub> | V    |

| VP1-TR            | Between PVIN1-PGND1 Pins, Transient 3 ns – 2.15 MHz (Note 1)                  | -0.3 | -      | 24                 | V    |

| VP2-TR            | Between PVIN2–PGND2 and PVIN3–PGND3 Pins, Transient 3 ns $-2.15$ MHz (Note 1) | -0.3 | -      | 7.0                | V    |

| VDG1              | Digital Pins: SDA, SCL, /INT (Note 1)                                         | -0.3 | -      | 6.0                | V    |

| VDG2              | Digital Pins: /RST (Note 1)                                                   | -0.3 | -      | V <sub>CORE</sub>  | V    |

| HBM               | ESD Withstand Voltage (Human Body Model) (Note 2)                             | 500  | -      | -                  | V    |

| CDM_CORNER        | ESD Withstand Voltage (CDM)<br>PVIN1, VINLDO, VOUTLDO, SW2, SW3, FB1 (Note 2) | 750  | -      | -                  | V    |

| CDM               | ESD Withstand Voltage (CDM) All Others Pins than Corners (Note 2)             | 500  | -      | -                  | V    |

| I <sub>LU</sub>   | LU Latch Up Current (Note 3)                                                  |      | 100    | -                  | mA   |

| T <sub>STG</sub>  | Storage Temperature Range                                                     | -65  | -      | 150                | °C   |

| T <sub>JMAX</sub> | Junction Temperature Range                                                    | -40  | -      | 170                | °C   |

| MSL               | Moisture Sensitivity (Note 4)                                                 | -    | Level1 | -                  |      |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

1. Refer to ELECTRICAL CHARACTERISTICS, RECOMMENDED OPERATING RANGES and/or APPLICATION INFORMATION for Safe Operating parameters.

This device series contains ESD protection and passes the following ratings: Human Body Model (HBM) ±500 V per JEDEC standard: JESD22–A114. Charged Device Model (CDM) 750 V (corner pins) and 500 V (others pins) per JEDEC standard: JESD22–C101 Class IV.

3. Latch up Current per JEDÈC standard: JESD78 class II.

4. Moisture Sensitivity Level (MSL): 1 per IPC/JEDEC standard: J-STD-020A.

## **RECOMMENDED OPERATING CONDITIONS**

| Symbol                  | Parameter                                                                                           | Min    | Тур   | Max   | Unit |

|-------------------------|-----------------------------------------------------------------------------------------------------|--------|-------|-------|------|

| P <sub>VIN1_RANGE</sub> | Power Input Supply                                                                                  | 4.6    | 9     | 18    | V    |

| V <sub>VIN_RANGE</sub>  | Power Input Supply                                                                                  | 2.8    | -     | 5.5   | V    |

| L <sub>OUT1</sub>       | Inductor for the PoC DC to DC Converter (Note 5)                                                    | -      | 2.2   | -     | μH   |

| L <sub>OUT2</sub>       | Inductor for the 1 A LV DC to DC Converter (Note 5)                                                 | -      | 1.0   | -     | μH   |

| L <sub>OUT3</sub>       | Inductor for the 500 mA LV DC to DC Converter (Note 5)                                              | -      | 1.0   | -     | μH   |

| C <sub>CORE</sub>       | Vcore Pin Capacitor (Note 5)                                                                        | 0.120* | 1     | -     | μF   |

| C <sub>PVIN1</sub>      | Input Capacitor for the PoC DC to DC Converter (Note 5)                                             | 3*     | 10**  | -     | μF   |

| C <sub>PVIN2</sub>      | Input Capacitor for the 1 A LV DC to DC Converter (Note 5)                                          | 5*     | 10**  | -     | μF   |

| C <sub>PVIN3</sub>      | Input Capacitor for the 500 mA LV DC to DC Converter (Note 5)                                       | 5*     | 10**  | -     | μF   |

| C <sub>VINLDO1</sub>    | Input Capacitor for the Internal LDO<br>V <sub>INLDO</sub> Connected to the DCDC1 Output (Note 5)   | -      | 0**   | -     | μF   |

| C <sub>VINLDO2</sub>    | Input Capacitor for the Internal LDO<br>V <sub>INLDO</sub> Connected to an External Supply (Note 5) | 1**    | 2.2** | -     | μF   |

| C <sub>OUT1</sub>       | Output Capacitor for PoC DC to DC Converter (Note 5)                                                | 6.4*   | 10**  | 100** | μF   |

| C <sub>OUT2</sub>       | Output Capacitor for the 1 A LV DC to DC Converter (Note 5)                                         | 5*     | 10**  | 100** | μF   |

| C <sub>OUT3</sub>       | Output Capacitor for 500 mA LV DC to DC Converter (Note 5)                                          | 5*     | 10**  | 100** | μF   |

| C <sub>OUTLDO</sub>     | Output Capacitor for the Internal LDO (Note 5)                                                      | 1.65*  | 2.2** | 47**  | μF   |

| ТJ                      | Junction Temperature Range (Note 6)                                                                 | -40    | 25    | +150  | °C   |

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

\* derated value.

\*\* nominal value.

5. Including de-ratings (Refer to the <u>Application Information</u> section of this document for further details)

6. The thermal shutdown set to 170°C (typical) avoids potential irreversible damage on the device due to power dissipation.

7. The R0JA is dependent of the PCB heat dissipation. Board used to drive this data was a NCV92100EVB board.

8. The maximum power dissipation (PD) is dependent by input voltage, maximum output current, pcb stack up and layout, and external components selected.

## THERMAL INFORMATION

| Symbol                    | Parameter                                                             | JEDEC<br>JESD51–3<br>(Calculated) | Demo<br>Board<br>(Measured) | Unit |

|---------------------------|-----------------------------------------------------------------------|-----------------------------------|-----------------------------|------|

| $\theta_{\text{J-C TOP}}$ | Thermal Resistance Junction to Case Top Resistance (Note 9)           | 27.6                              | -                           | °C/W |

| $\theta_{JB}$             | Thermal Resistance Junction to Bottom Top Resistance (Note 10)        | 1.6                               | -                           | °C/W |

| $\theta_{JA}$             | Thermal Resistance Junction to Ambient QFNW20 on Demo-board (Note 11) | 31                                | 35                          | °C/W |

9. Calculated with infinite heatsink affixed to case top without any board present.

10. Calculated with infinite heatsink affixed to case bottom without any board present.

11. The R0JA is dependent of the PCB heat dissipation. Board used to drive this data was a NCV92100EVB board.

**ELECTRICAL CHARACTERISTICS** (Refer to the <u>Application Information</u> section of this data sheet for more details. Min and Max Limits apply for  $T_J = -40^{\circ}$ C to  $+150^{\circ}$ C,  $V_{IN}$  range (PVIN\_RANGE and VIN\_RANGE) and default configuration, unless otherwise specified. Typical values are referenced to  $T_J = +25^{\circ}$ C,  $V_{IN}$  = range and default configuration, unless otherwise specified.)

| Symbol                     | Parameter                                                                   | Min    | Тур   | Мах    | Unit |

|----------------------------|-----------------------------------------------------------------------------|--------|-------|--------|------|

| SUPPLY CURRE               | NT: PIN VIN                                                                 |        |       |        |      |

| Ι <sub>Q</sub>             | Operating Quiescent Current, No Load Vin = 9 V, Default<br>Configuration    | -      | 13    | -      | mA   |

| INTERNAL VOLT              | TAGE REFERENCE                                                              |        |       |        |      |

| V <sub>CORE</sub>          | Internal Voltage Reference for Core Supply                                  | 4.37   | 4.8   | 4.9    | V    |

| DCDC1 (PoC DC              | DC CONVERTER)                                                               |        |       |        |      |

| V <sub>OUT1</sub>          | Output Voltage Accuracy Vin Range, lout Range                               | -1.5   | -     | +1.5   | %    |

| V <sub>OUT1_33_100mA</sub> | Default Output Voltage Vin = 9 V, lout = 100 mA                             | 3.2505 | 3.3   | 3.3495 | V    |

| D <sub>MAX1</sub>          | Maximum Duty Cycle                                                          | -      | 92    | -      | %    |

| DC <sub>LOAD1</sub>        | Load Regulation, lout from 100 mA to 1 A                                    | -      | 0.05  | -      | %/A  |

| DC <sub>LINE1</sub>        | Line Regulation, Vin from 5 V to 18 V, lout = 100 mA                        | -      | 0.001 | -      | %/V  |

| I <sub>OUTMAX1</sub>       | Output Current Range (Note 12)                                              | 1.2    | -     | -      | Α    |

| I <sub>LIMP1</sub>         | Output Peak Current High Side Switch (Note 12)                              | 1.5    | 1.8   | 2.1    | Α    |

| I <sub>LIMN1</sub>         | Output Peak Current Low Side Switch (Note 12)                               | -      | 1     | -      | Α    |

| R <sub>ON_H1</sub>         | High-Side MOSFET ON Resistance                                              | -      | 385   | -      | mΩ   |

| R <sub>ON_L1</sub>         | Low-Side MOSFET ON Resistance                                               | -      | 250   | -      | mΩ   |

| R <sub>DIS1</sub>          | Internal Active Output Discharge, from FB to PGND Vout = 3.3 V              | -      | 80    | -      | Ω    |

| DCDC2 (1 A LV I            | DCDC CONVERTER)                                                             |        |       |        |      |

| V <sub>OUT21</sub>         | Output Voltage Accuracy<br>Vin Range, Vout Range, Iout Range                | -1     | -     | +1     | %    |

| VOUT2_12_100mA             | Default Output Voltage Vin = 3.3 V, lout = 100 mA                           | 1.188  | 1.2   | 1.212  | V    |

| DC <sub>LOAD2</sub>        | Load Regulation, lout from 100 mA to 1 A                                    | -      | 0.05  | -      | %/A  |

| DC <sub>LINE2</sub>        | Line Regulation, Vin from 2.8 V to 5.5 V, lout = 100 mA                     | -      | 0.001 | -      | %/V  |

| I <sub>OUTMAX2</sub>       | Output Current Range (Note 12)                                              | 1      | -     | -      | Α    |

| I <sub>LIMP2</sub>         | Output Peak Current High Side Switch<br>P <sub>VIN2</sub> = 3.3 V (Note 12) | 1.65   | 2.0   | 2.35   | A    |

| I <sub>LIMN2</sub>         | Output Peak Current Low Side Switch<br>P <sub>VIN2</sub> = 3.3 V (Note 12)  | -      | 1.2   | -      | A    |

| R <sub>ON_H2</sub>         | High-Side MOSFET ON Resistance                                              | -      | 120   | -      | mΩ   |

| R <sub>ON_L2</sub>         | Low-Side MOSFET ON Resistance                                               | -      | 90    | -      | mΩ   |

| R <sub>DIS2</sub>          | Internal Active Output Discharge, from FB to PGND Vout = 1.2 V              | -      | 100   | -      | Ω    |

| DCDC3 (500 mA              | LV DCDC CONVERTER)                                                          |        |       |        |      |

| V <sub>OUT31</sub>         | Output Voltage Accuracy<br>Vin Range, Vout Range, Iout Range                | -1     | _     | +1     | %    |

| VOUT3_18_100mA             | Default Output Voltage Vin = 3.3 V, lout = 100 mA                           | 1.782  | 1.8   | 1.818  | V    |

| DC <sub>LOAD3</sub>        | Load Regulation, lout from 100 mA to 500 mA                                 | -      | 0.05  | -      | %/A  |

| DC <sub>LINE3</sub>        | Line Regulation, Vin from 2.8 V to 5.5 V, lout = 100 mA                     | -      | 0.001 | -      | %/V  |

| I <sub>OUTMAX3</sub>       | Output Current Range (Note 12)                                              | 0.5    | -     | -      | Α    |

| I <sub>LIMP3</sub>         | Output Peak Current High Side Switch<br>P <sub>VIN3</sub> = 3.3 V (Note 12) | 1.35   | 1.7   | 2.05   | A    |

| I <sub>LIMN3</sub>         | Output Peak Current Low Side Switch<br>P <sub>VIN3</sub> = 3.3 V (Note 12)  | -      | 1.2   | -      | A    |

| R <sub>ON_H3</sub>         | High-Side MOSFET ON Resistance                                              | _      | 220   | _      | mΩ   |

**ELECTRICAL CHARACTERISTICS** (Refer to the <u>Application Information</u> section of this data sheet for more details. Min and Max Limits apply for  $T_J = -40^{\circ}$ C to  $+150^{\circ}$ C,  $V_{IN}$  range (PVIN\_RANGE and VIN\_RANGE) and default configuration, unless otherwise specified. Typical values are referenced to  $T_J = +25^{\circ}$ C,  $V_{IN}$  = range and default configuration, unless otherwise specified.) (continued)

| Symbol                  | Parameter                                                                                                             | Min  | Тур   | Max  | Unit |

|-------------------------|-----------------------------------------------------------------------------------------------------------------------|------|-------|------|------|

| DCDC3 (500 mA           | LV DCDC CONVERTER)                                                                                                    |      |       |      |      |

| R <sub>ON_L3</sub>      | Low-Side MOSFET ON Resistance                                                                                         | -    | 145   | -    | mΩ   |

| R <sub>DIS3</sub>       | Internal Active Output Discharge, from FB to PGND Vout = 1.8 V                                                        | -    | 100   | _    | Ω    |

| LOW DROPOUT             | REGULATOR                                                                                                             |      |       |      |      |

| I <sub>OUTLDO_1</sub>   | Maximum Output Current, V <sub>IN R</sub> ange, V <sub>OUT</sub> $\leq$ V <sub>IN</sub> $-$ 200 mV (Note 12)          | 300  | -     | _    | mA   |

| I <sub>LIMITLDO</sub>   | Current Limit, V <sub>INLDO</sub> = 3.1 V, V <sub>OUTLDO</sub> = 2.8 V                                                | 350  | -     | 620  | mA   |

| $\Delta V_{OUT\_LDO_1}$ | Output Voltage Accuracy, V <sub>IN</sub> = 3.3 V, V <sub>OUT</sub> = 2.8 V No Load                                    | -1.0 | VNOM  | +1.0 | %    |

| $\Delta V_{OUT\_LDO_2}$ | Output Voltage Accuracy, VINLDO Range, IOUTLDO Range                                                                  | -1.0 | VNOM  | +1.0 | %    |

| DC <sub>LOADLDO</sub>   | Load Regulation, I <sub>OUT</sub> = 0 mA to 200 mA                                                                    | _    | 0.04  | _    | %    |

| DC <sub>LINELDO</sub>   | Line Regulation, V <sub>INLDO</sub> = 3.1 V to 5.5 V I <sub>OUTLDO</sub> = 200 mA                                     | _    | 0.04  | _    | %    |

| V <sub>DROP</sub>       | Dropout Voltage, VOUT = 2.8 V, I <sub>OUT</sub> = 300 mA                                                              | 80   | 110   | 210  | mV   |

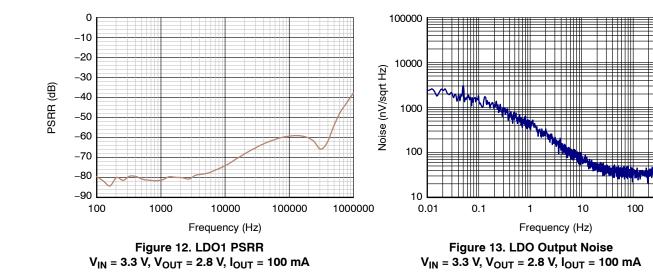

| PSRR_1k                 | Ripple Rejection, F = 1 kHz<br>V <sub>INLDO</sub> = 3.3 V, V <sub>OUTLDO</sub> = 2.8 V, I <sub>OUTLDO</sub> = 100 mA  | -    | -80   | -    | dB   |

| PSRR_10k                | Ripple Rejection, F = 10 kHz<br>V <sub>INLDO</sub> = 3.3 V, V <sub>OUTLDO</sub> = 2.8V, I <sub>OUTLDO</sub> = 100 mA  | _    | -75   | -    | dB   |

| PSRR_100k               | Ripple Rejection, F = 100 kHz<br>V <sub>INLDO</sub> = 3.3 V, V <sub>OUTLDO</sub> = 2.8V, I <sub>OUTLDO</sub> = 100 mA | _    | -60   | -    | dB   |

| PSRR_1M                 | Ripple Rejection, F = 1 MHz<br>V <sub>INLDO</sub> = 3.3 V, V <sub>OUTLDO</sub> = 2.8V, I <sub>OUTLDO</sub> = 100 mA   | _    | -35   | -    | dB   |

| Noise                   | Output Noise, 10 Hz $\rightarrow$ 100 kHz $V_{OUTLDO}$ = 2.8 V                                                        | -    | 34    | _    | μV   |

| R <sub>DISLDO</sub>     | LDO Active Output Discharge, V <sub>OUT</sub> = 2.8 V                                                                 | -    | 105   | _    | Ω    |

| UVLO AND OVL            | 0                                                                                                                     |      |       |      |      |

| V <sub>INUV-</sub>      | $V_{\text{IN}}$ UVLO Falling Threshold, $P_{\text{VIN1}}$ Pin, Default Setting                                        | 5    | 5.1   | _    | V    |

| V <sub>INUV+</sub>      | V <sub>IN</sub> UVLO Rising Threshold, P <sub>VIN1</sub> Pin, Default Setting                                         |      | 6.8   | 7    | V    |

| VINUVRANGE              | $V_{\text{IN}}$ UVLO Falling Threshold, $P_{\text{VIN1}}$ Pin, Programmability Range (See Table x)                    | 4.35 | -     | 7    | V    |

| VINUV+_RANGE            | $V_{\text{IN}}$ UVLO Rising Threshold, $P_{\text{VIN1}}$ Pin, Programmability Range (See Table x)                     | 4.5  | -     | 8    | V    |

| V <sub>INOV+</sub>      | V <sub>IN</sub> OVF Rising Threshold, P <sub>VIN1</sub> Pin                                                           | 18   | 18.3  | 18.6 | V    |

| VINOVHYST               | V <sub>IN</sub> OVF Hysteresis                                                                                        | _    | 204   | _    | mV   |

| V <sub>INOVDBN</sub>    | V <sub>IN</sub> OVF Debounce Time, P <sub>VIN1</sub> Pin                                                              | -    | 10    | _    | μs   |

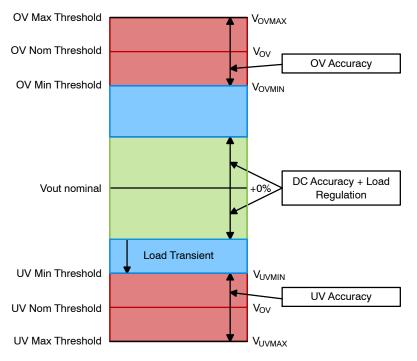

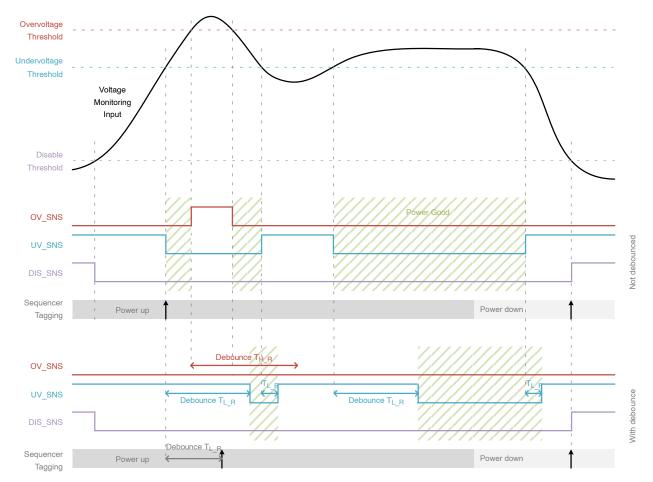

| WINDOWS VOL             | TAGE MONITORING                                                                                                       |      |       |      |      |

| VL                      | Undervoltage Detection Threshold, Programmability (3 Bits)                                                            | -10  | -     | -3   | %    |

| V <sub>H</sub>          | Overvoltage Detection Threshold, Programmability (3 Bits)                                                             | 3    | -     | 10   | %    |

| V <sub>LH</sub>         | Undervoltage Detection Hysteresis, $V_{OUT} \le 2.2 V$                                                                | -    | 4.5   | 7.6  | mV   |

| V <sub>HH</sub>         | Overvoltage Detection Hysteresis, $V_{OUT} \le 2.2 V$                                                                 | _    | 4.5   | 7.6  | mV   |

| V <sub>LH SC</sub>      | Undervoltage Detection Hysteresis, V <sub>OUT</sub> > 2.2 V                                                           | _    | 11.25 | 19   | mV   |

| V <sub>HH_SC</sub>      | Overvoltage Detection Hysteresis, V <sub>OUT</sub> > 2.2 V                                                            | _    | 11.25 | 19   | mV   |

| D <sub>ACC1</sub>       | Detection Accuracy, 0.6 V $\leq$ V <sub>OUT</sub> < 1 V                                                               | -10  | -     | 10   | mV   |

| D <sub>ACC2</sub>       | Detection Accuracy, V <sub>OUT</sub> ≥ 1 V                                                                            | -1   | -     | 1    | %    |

| T <sub>L_R</sub>        | Undervoltage Detection Debounce Programmability, Rising Edge                                                          | 32   | _     | 256  | μs   |

**ELECTRICAL CHARACTERISTICS** (Refer to the <u>Application Information</u> section of this data sheet for more details. Min and Max Limits apply for  $T_J = -40^{\circ}$ C to  $+150^{\circ}$ C,  $V_{IN}$  range (PVIN\_RANGE and VIN\_RANGE) and default configuration, unless otherwise specified. Typical values are referenced to  $T_J = +25^{\circ}$ C,  $V_{IN}$  = range and default configuration, unless otherwise specified.) (continued)

| Symbol                    | Symbol Parameter                                                                                                       |                                  |       | Max  | Unit |

|---------------------------|------------------------------------------------------------------------------------------------------------------------|----------------------------------|-------|------|------|

| WINDOWS VOL               | rage monitoring                                                                                                        | - <b>-</b>                       |       | -    | -    |

| T <sub>L_F</sub>          | Undervoltage Detection Debounce Programmability, Falling Edge                                                          | 0                                | -     | 128  | μs   |

| T <sub>H_R</sub>          | Overvoltage Detection Debounce Programmability, Rising Edge                                                            | 0                                | _     | 128  | μs   |

| T <sub>H_F</sub>          | Overvoltage Detection Debounce Programmability, Falling Edge                                                           | 32                               | _     | 256  | μs   |

| VDISABLE_DCDC1            | Disable Detection Threshold DCDC1                                                                                      | - 1                              | 2000  | -    | mV   |

| VDISABLE_DCDC2            | Disable Detection Threshold DCDC2                                                                                      | -                                | 600   | -    | mV   |

| VDISABLE_DCDC3            | Disable Detection Threshold DCDC3                                                                                      | -                                | 600   | -    | mV   |

| V <sub>DISABLE</sub> LDO1 | Disable Detection Threshold LDO1                                                                                       | -                                | 100   | -    | mV   |

| TURN ON TIME              | AND SOFT-START                                                                                                         |                                  |       |      |      |

| T <sub>SS</sub>           | Turn ON time, Default Setting, from PVIN1 to Power Up Sequence Start                                                   | -                                | 5.12  | -    | ms   |

| T <sub>SS1</sub>          | Soft-start Time DCDC1, Time from 10% to 90% of Output Voltage Target (Default Setting), Vout = 3.3 V                   | -                                | 0.845 | -    | ms   |

| T <sub>SS2</sub>          | Soft-start Time DCDC2, Time from 10% to 90% of Output Voltage Target (Default Setting), Vout = 1.2 V                   | -                                | 0.31  | -    | ms   |

| T <sub>SS3</sub>          | Soft-start Time DCDC3, Time from 10% to 90% of Output Voltage Target (Default Setting), Vout = 1.8 V                   | -                                | 0.45  | -    | ms   |

| T <sub>SS4</sub>          | Soft–start Time LDO, Time from 10% to 90% of Output Voltage Target (Default Setting), Vout = 2.8 V, COUT = 2.2 $\mu F$ | -                                | 1.45  | -    | ms   |

| INTERNAL CLO              | CKS                                                                                                                    | 1                                |       |      |      |

| CLK <sub>SYSOSC</sub>     | Internal System Clock                                                                                                  | 1.86                             | 2.00  | 2.14 | MHz  |

| F <sub>SW</sub>           | DCDC Switching Frequency                                                                                               | 2                                | 2.15  | 2.3  | MHz  |

| $\Phi_{	t DCDC2}$ DCDC1   | Phase Shift between DCDC2 and DCDC1                                                                                    | -                                | 120   | -    | 0    |

| ΦDCDC3 DCDC1              | Phase Shift between DCDC3 and DCDC1                                                                                    | -                                | 240   | -    | 0    |

| THERMAL SHUT              | rdown                                                                                                                  |                                  |       |      |      |

| T <sub>SD</sub>           | Thermal Shutdown                                                                                                       | -                                | 163   | -    | °C   |

| T <sub>WNG</sub>          | Thermal Warning                                                                                                        | -                                | 152   | -    | °C   |

| T <sub>WNGH</sub>         | Thermal Warning Hysteresis                                                                                             | -                                | 10    | -    | °C   |

| T <sub>PWNG</sub>         | Thermal Pre-Warning (Default)                                                                                          | -                                | 138   | -    | °C   |

| T <sub>PWNGH</sub>        | Thermal Pre-Warning Hysteresis (Default)                                                                               | -                                | 6     | -    | °C   |

| T <sub>GATING</sub>       | Thermal Gating Threshold / Thermal Shutdown Low Threshold                                                              | -                                | 125   | -    | °C   |

| /RST AND /INT F           | PINS (PUSH-PULL)                                                                                                       |                                  |       |      |      |

| V <sub>INT_L</sub>        | /INT Pin Low Voltage, I <sub>INT</sub> = 3 mA                                                                          | -                                | -     | 0.3  | V    |

| V <sub>INT_H1</sub>       | /INT Pin High Voltage, $I_{INT}$ = –3 mA $V_{OUT}$ $\geq$ 1.2 V                                                        | V <sub>OUT_DCDC3</sub><br>x 0.65 | _     | _    | V    |

| V <sub>INT_H2</sub>       | /INT Pin High Voltage, I <sub>INT</sub> = -3 mA V <sub>OUT</sub> < 1.2 V                                               | V <sub>OUT_DCDC3</sub><br>- 0.45 | -     | -    | V    |

| V <sub>RST_L</sub>        | /RST Pin Low Voltage, I <sub>RST</sub> = 3 mA                                                                          | -                                | -     | 0.3  | V    |

| V <sub>RST_H1</sub>       | /RST Pin High Voltage, $I_{RST} = -3 \text{ mA V}_{OUT} \ge 1.2 \text{ V}$                                             | V <sub>OUT_DCDC3</sub><br>x 0.65 | -     | -    | V    |

| V <sub>RST_H2</sub>       | /RST Pin High Voltage, I <sub>RST</sub> = -3 mA V <sub>OUT</sub> < 1.2 V                                               | V <sub>OUT_DCDC3</sub><br>- 0.45 | _     | _    | V    |

**ELECTRICAL CHARACTERISTICS** (Refer to the <u>Application Information</u> section of this data sheet for more details. Min and Max Limits apply for  $T_J = -40^{\circ}$ C to  $+150^{\circ}$ C,  $V_{IN}$  range (PVIN\_RANGE and VIN\_RANGE) and default configuration, unless otherwise specified. Typical values are referenced to  $T_J = +25^{\circ}$ C,  $V_{IN}$  range and default configuration, unless otherwise specified.) (continued)

| Symbol                     | Parameter                                                                    | Min  | Тур | Max  | Unit |

|----------------------------|------------------------------------------------------------------------------|------|-----|------|------|

| I <sup>2</sup> C INTERFACE |                                                                              |      |     |      |      |

| V <sub>I2C_H</sub>         | SCL and SDA Input Logic High (Note 13, 14, 15)                               | 1.15 | -   | -    | V    |

| V <sub>I2C_L</sub>         | SCL and SDA Input Logic Low (Note 16)                                        | -    | -   | 0.45 | V    |

| V <sub>SDAO_L</sub>        | SDA Output Active Low, Sink 15 mA (Note 17)                                  | -    | -   | 0.4  | V    |

| I <sub>SDAO_H</sub>        | SDA Output Open Drain Leakage, 5.5 V                                         |      | -   | 500  | nA   |

| F <sub>I2C</sub>           | SCL Clock Frequency, 1.8 V Supplied I/O Rail (Note 13, 17, 18)               | 0    | -   | 1    | MHz  |

| I2C <sub>SS</sub>          | Pulse Width of Spikes that Must Be Suppressed by the Pinout Filter (Note 19) | -    | -   | 50   | ns   |

| C <sub>I2C</sub>           | SCL and SDA Input Pin Capacitance                                            | -    | 5   | -    | pF   |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

12. Junction temperature must be maintained below 150°C. Output load current capability depends on the application thermal capability.

13. In support of Fast Mode Plus, 1.8 V supplied I/O rails and the related 100 mV of drop totaling 1.7 V minimum.

14. For any input voltage greater than the minimum value indicated the signal is guaranteed detected high.

15. I<sup>2</sup>C typical VIO 1.8 V to 3.3 V.

16. For any input voltage smaller than the maximum value indicated the signal is guaranteed detected low.

17. Fast Mode Plus fall time (tf) and rise time (tr) required (120 ns maximum).

18.I<sup>2</sup>C bus frequency may be adjusted depending on the actual operating voltage, pull-up resistance, bus capacitance (which could be up to 400 pF) and master GPIO driver strength.

19. Input filters on the SDA and SCL inputs suppress noise spikes of less than 50 ns.

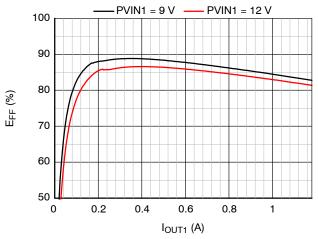

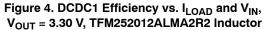

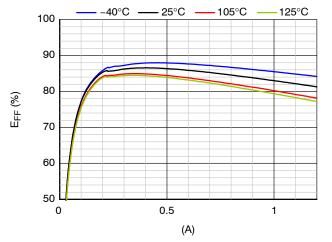

## **TYPICAL OPERATING CHARACTERISTICS**

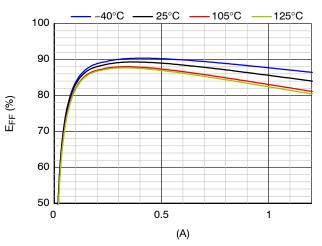

$(PV_{IN1} = 9 \text{ V} \text{ (Unless otherwise noted)}. T_A = +25^{\circ}C, DCDC2 = 1.20 \text{ V}, DCDC2 = 1.3 \text{ V}, LDO1 = 2.8 \text{ V}, C_{LDO} = 2.2 \mu\text{F} 0603, L_{DCDC} = 1.0 \mu\text{H} (2016) - C_{DCDC} = 10 \mu\text{F} 0603 / X7T)$

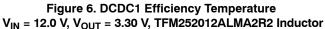

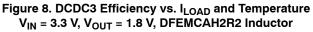

Figure 5. DCDC1 Efficiency Temperature  $V_{IN}$  = 9.0 V,  $V_{OUT}$  = 3.30 V, TFM252012ALMA2R2 Inductor

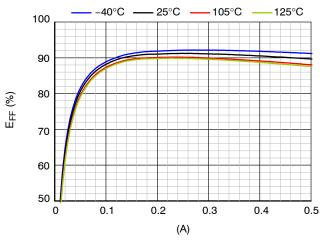

Figure 7. DCDC2 Efficiency vs.  $I_{LOAD}$  and Temperature  $V_{IN}$  = 3.3 V,  $V_{OUT}$  = 1.2 V, DFEMCAH2R2 Inductor

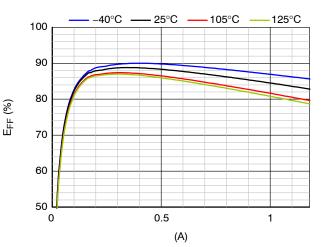

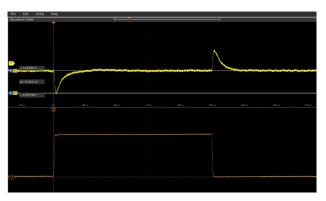

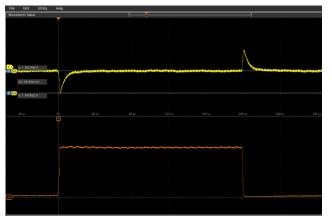

Figure 9. DCDC1 Load Transient VIN = 9 V, VOUT = 3.3 V, ILOAD from 10 mA to 1A

## **TYPICAL OPERATING CHARACTERISTICS**

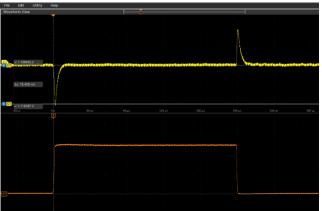

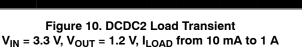

$(PV_{IN1} = 9 V (Unless otherwise noted). T_A = +25^{\circ}C, DCDC2 = 1.20 V, DCDC2 = 1.3 V, LDO1 = 2.8 V, C_{LDO} = 2.2 \mu F 0603, L_{DCDC} = 1.0 \mu H (2016) - C_{DCDC} = 10 \mu F 0603 / X7T) (Continued)$

Figure 11. DCDC3 Load Transient  $V_{IN}$  = 3.3 V,  $V_{OUT}$  = 1.8 V,  $I_{LOAD}$  from 10 mA to 500 mA

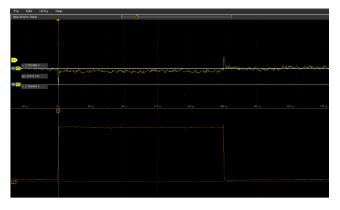

Figure 14. LDO1 Load Transient  $V_{\rm IN}$  = 3.3 V,  $V_{\rm OUT}$  = 2.8 V,  $I_{\rm LOAD}$  from 10 mA to 300 mA

1000

#### DETAILED OPERATING DESCRIPTION

#### General

The NCV92310 is optimized to supply cameras of automotive Power over Coax applications.

It integrates one Power Over Coax switched mode DCDC converters, two low voltage switched mode DCDC converters and one low dropout linear regulator. The IC is widely programmable through an I<sup>2</sup>C interface with a default setting provided by the internal OTP memory set during the manufacturing process. The core of the NCV92310 is supplied from PVIN1 from where a low voltage core voltage VCORE is derived. The VCORE supplies most of the on-chip analog and digital circuitry. PVIN1 can be supplied from a 5 V regulated source or connected directly to the filtered power over coax supply.

The output voltage range, current capabilities and performances of the switched mode DCDC converters are well suited to supply a camera module. For PWM operation, the converters run on a local 2.15 MHz. All the switching components are integrated including the compensation networks and synchronous rectifier. Only a small size inductor (2.2  $\mu$ H for the PoC DCDC and 1  $\mu$ H for the LV DCDCs) and 10  $\mu$ F bypass capacitor are required for typical applications. Higher output capacitor value may be needed depending on the load transient requirement.

The low noise low dropout regulator can be used to supply the lower power rails in the application. The regulator is bypassed with a small size 2.2  $\mu$ F capacitor. Higher output capacitor value may be needed depending on the load transient requirement.

The low voltage regulators (DCDC2, DCDC3, LDO1) each have their own input supply pin to be able to connect it either independently to the system supply rail or to the DCDC converter output, in the application. Like DCDC1, each converter and LDO is enabled smoothly with a controlled ramp up in order to avoid any inrush current.

All supply rails are monitored by on-chip voltage window monitors. The window size and detection speed are programmable. When a monitor is tripped, an interrupt is generated and shutdown scenarios can be engaged. The monitors are also used to verify if the order of the power up and power down sequences are respected. Both mechanisms are essential in reaching a high level of functional safety.

The overall operation of the NCV92310 PMIC is governed by a state machine that will handle the initialization of the IC and the built–in self–test, the fault states, and the different operating modes.

All regulators include an active output discharge which can be independently enabled / disabled by the appropriate settings in the DIS register (refer to the register definition section). However to prevent any disturbances on the power-up sequence, a quick active output discharge is done during the start-up sequence for all output channels.

#### **DCDCs PWM Mode Operation**

All internal DCDCs operate in PWM mode from a fixed clock and adapts its duty cycle to regulate the desired output voltage. In this mode, the inductor current is in CCM and the voltage is regulated by PWM. The internal low side switch operates as synchronous rectifier and is driven complementary to the high side switch. In CCM, the lower side switch in a synchronous converter provides a lower voltage drop than the diode in an asynchronous converter, which provides less loss and higher efficiency.

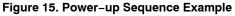

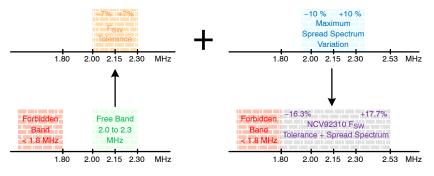

#### **DCDCs Switching Clock and Spread Spectrum**

Switching Clock of the 3 DCDCs operates at 2.15 MHz. To avoid a too high inrush current, a phase shift is applied for each DCDC converter (DCDC1: 0°, DCDC2: 120°, DCDC3: 240°)

In order to optimize the peak emission of the DC to DC converters switching frequency, a frequency spreading option allows to spread the switching frequency of the converters which can be useful in meeting system EMI requirements. This option, available with on chip internal oscillator, is factory programmable and can be changed thru  $I^2C$ .

NCV92310 integrates a random spread spectrum (16 frequencies) with OTPs and  $I^2C$  programmable tolerance (5% max and 10% max).

Figure 16. Tolerance + Spread Spectrum with Spread = 10% Max

Different spread spectrum modulations are available based on 16 frequency bins. By default, the triangular double peak modulation is used with OTPs and  $I^2C$ programmable tolerance ( $\pm 5\%$  max,  $\pm 10\%$  max). The frequency change can occur every n buck cycles (n is spread spectrum modulation divider from 1 to 128). Resulting modulation frequency is

$$F_{M} = \frac{F_{SW}}{n \times 32}$$

(eq. 1)

(with n is spread spectrum modulation divider)

Figure 17. Tolerance + Spread Spectrum with Spread = 10% Max

Pseudorandom modulation with 16 bits pattern is also available.

#### Low Dropout Regulator

Internal LDO is a low noise, high PSRR and high bandwidth regulator intended to supply image sensor analog pixel input.

Its extended bandwidth allows best in class load transient performances, which helps improve image quality.

Internal LDO limit the output current at 90 mA worst case ( $I_{LDO\_STARTUP}$ ) during the startup phase. LDO soft start setting and total output capacitor connected at the VOUTLDO is selected by the following equation:

Cout\_ldo\_max = IIdo\_startup

$$\times \frac{\Delta t}{\Delta V}$$

(eq. 2)

If C<sub>OUT\_LDO</sub> exceed C<sub>OUT\_LDO\_MAX</sub>, internal short circuit protection may be triggered.

#### Soft Start Time Setting

Soft start timing is set thru I<sup>2</sup>C and On Time Programmable internal memory.

#### Table 1. SOFT START SETTINGS

| Buck Soft Start Time (ms)                           | LDO Soft Start Time (ms)                   |

|-----------------------------------------------------|--------------------------------------------|

| 0.64 <sub>(ms/V)</sub> x V <sub>OUT</sub>           | 1.28 <sub>(ms/V)</sub> x V <sub>OUT</sub>  |

| 0.32 <sub>(ms/V)</sub> x V <sub>OUT</sub> (default) | $0.64_{(ms/V)} \times V_{OUT}$ (default)   |

| 0.16 <sub>(ms/V)</sub> x V <sub>OUT</sub>           | 0.32 <sub>(ms/V)</sub> x V <sub>OUT</sub>  |

| 0.08 <sub>(ms/V)</sub> x V <sub>OUT</sub>           | 0.16 <sub>(ms/V</sub> ) x V <sub>OUT</sub> |

It allows limiting the inrush current at the input during the power–up sequence.

#### **Regulator Stability**

#### DCDC Regulators

DCDC1, DCDC2 and DCDC3 use a voltage mode architecture. Regulators stability depends on the output LC filter.

Each regulator embeds an OTP bit that allow managing the stability versus the total output capacitor value. With the default inductor value (DCDC1 =  $2.2 \mu$ H, DCDC2 and DCDC3 =  $1 \mu$ H), output capacitor range without derating is:

- $10 \ \mu\text{F}$  to  $50 \ \mu\text{F}$  (default setting).

- 50 µF to 100 µF.

#### Low Dropout Regulator

Bandwidth of the low dropout regulator has been adapted to improve the load transient response. In case lower ripple is required, internal LDO of the NCV92310 allows using high output capacitor value. In that case, internal stability has to be set thru OTP:

- Up to 50 μF (default setting).

- 50 µF to 100 µF.

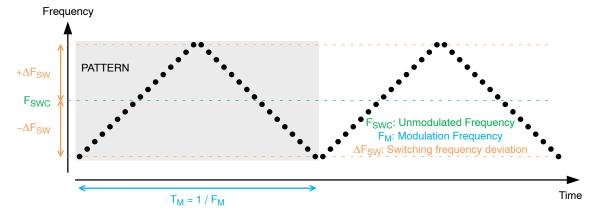

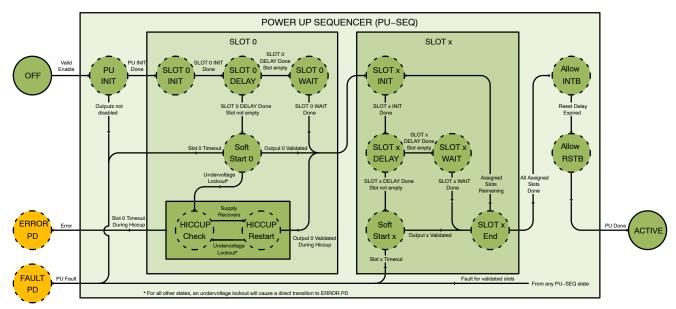

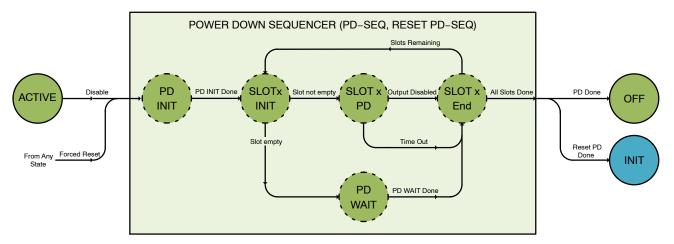

# STATE MACHINE

The overall operation of the NCV92310 is governed by a state machine that handles the initialization of the IC and the built–in self–test, the fault states, and the different operating modes.

The below diagram represents the behavior as described in the remainder of this document.

Figure 18. Default State Machine

The state machine is comprised of a number of states of which some are only transitional. The state machine transitions from state to state based on certain specific conditions. Below tables provide a detailed description of each of the states as well as of the transitions.

## Table 2. STATE MACHINE STATES

| Group                     | State           | Туре         | RSTB       | INTB       | l <sup>2</sup> C | Description                                                                                                                                         |

|---------------------------|-----------------|--------------|------------|------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| NO POWER                  | -               | -            | -          | -          | -                | The supply conditions on PVIN1 and VCORE are too low for the state machine to operate.                                                              |

| INITIALIZATION            | RESET           | Steady       | L          | L          | No               | Only the logic circuitry has sufficient supply and is being held in reset.                                                                          |

|                           | INIT            | Transitional | L          | L          | No               | Upon entry, all logic is reset to default and OTP content is loaded. The analog circuitry is enabled.                                               |

|                           | BIST            | Transitional | L          | L          | No               | Upon entry, a built-in self-test is started                                                                                                         |

| OPERATIONAL               | OFF             | Steady       | L          | Ι          | R/W              | The IC is biased and ready to accept a power up sequence request                                                                                    |

|                           | ACTIVE          | Steady       | R          | I          | R/W              | A power up sequence has been executed and the IC is operating normally                                                                              |

|                           | ACTIVE<br>FLAG  | Transitional | R          | L          | R/W              | Similar to ACTIVE but a flag is raised and upon<br>entry a flag timer starts running                                                                |

|                           | PU-SEQ          | Transitional | See<br>PUS | See<br>PUS | R only           | Upon entry, a power up sequence is started.                                                                                                         |

|                           | PD-SEQ          | Transitional | See<br>PDS | See<br>PDS | R only           | Upon entry, a power down sequence is started                                                                                                        |

| ERROR & FAULT<br>HANDLING | RESET<br>PD-SEQ | Transitional | L          | Ι          | R only           | Upon entry, a power down sequence is started                                                                                                        |

|                           | FAULT PD        | Transitional | L          | I          | R only           | Upon entry, all supplies are powered down<br>simultaneously. Internal delay equal to PDS Time<br>Out delay is integrated before going to next state |

|                           | ERROR PD        | Transitional | L          | I          | R only           | Upon entry, all supplies are powered down simultaneously                                                                                            |

|                           | LOCK            | Steady       | L          | I          | R/W              | The state machine is in the safe state with all supplies disabled.                                                                                  |

|                           | INVALID         | Steady       | L          | I          | No               | Upon entry, an emergency powered down is initiated and product set in reset.                                                                        |

L means Low, R means Released, I reflect the actual state of the Interrupts

## Table 3. STATE MACHINE TRANSITIONS

| Transition                      | From                    | То                      | Description                                                                                                                                                                                                                                                                                        |

|---------------------------------|-------------------------|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Application of<br>Logic Power   | NO POWER                | RESET                   | PVIN1 becomes greater than the logic undervoltage detection level                                                                                                                                                                                                                                  |

| Application of<br>Analog Power  | RESET                   | INIT                    | PVIN1 becomes greater than the PVIN1 undervoltage lockout detection level                                                                                                                                                                                                                          |

| INIT Done                       | INIT                    | BIST                    | The initialization has been finished                                                                                                                                                                                                                                                               |

| BIST OK                         | BIST                    | OFF                     | The built-in self-test was successful                                                                                                                                                                                                                                                              |

| BIST Failure                    | BIST                    | LOCK                    | The built-in self-test failed, and the BIST error counter has reached its limit                                                                                                                                                                                                                    |

| Retry                           | BIST                    | BIST                    | The built-in self-test failed, the BIST error counter has not reached its limit, and a new built in self-test is started                                                                                                                                                                           |

| Valid Enable                    | OFF                     | PU-SEQ                  | A power up sequence is requested through I <sup>2</sup> C                                                                                                                                                                                                                                          |

| PU Done                         | PU-SEQ                  | ACTIVE                  | The power up sequence has been executed and no faults are detected in the sequencing                                                                                                                                                                                                               |

| PU Fault                        | PU-SEQ                  | FAULT PD                | A fault is detected during the power up sequence                                                                                                                                                                                                                                                   |

| Flag                            | ACTIVE                  | ACTIVE FLAG             | An event occurred and is signaled to the host through INTB                                                                                                                                                                                                                                         |

| Flag Cleared                    | ACTIVE FLAG             | ACTIVE                  | The signaled event is cleared by the host through I <sup>2</sup> C before a time out occurs                                                                                                                                                                                                        |

| Time Out Fault                  | ACTIVE FLAG             | FAULT PD                | The signaled event is not cleared in time by the host                                                                                                                                                                                                                                              |

| Disable                         | ACTIVE &<br>ACTIVE FLAG | PD-SEQ                  | A power down sequence is requested through I <sup>2</sup> C                                                                                                                                                                                                                                        |

| PD Done                         | ACTIVE &<br>ACTIVE FLAG | OFF                     | The power down sequence has been executed                                                                                                                                                                                                                                                          |

| Reset PD Done                   | RESET PD-SEQ            | INIT                    | The power down sequence has been executed                                                                                                                                                                                                                                                          |

| Soft Reset                      | ACTIVE &<br>ACTIVE FLAG | ACTIVE &<br>ACTIVE FLAG | The RSTB pin is temporarily made low by the Watchdog engine, or upon request through $\mathrm{I}^{2}\mathrm{C}$                                                                                                                                                                                    |

| Fault                           | ACTIVE &<br>ACTIVE FLAG | FAULT PD                | A fault is detected that necessitates a power down                                                                                                                                                                                                                                                 |

| Forced reset                    | Any State               | RESET PD-SEQ            | A power down sequence is requested through I <sup>2</sup> C.                                                                                                                                                                                                                                       |

| Error                           | Any State               | ERROR PD                | An abnormal operation condition has occurred which necessitates a power down                                                                                                                                                                                                                       |

| Fatal Error                     | Any State               | INVALID                 | A short circuit condition is detected at VCORE or an internal clock error<br>occurs                                                                                                                                                                                                                |

| Removal of Logic                | Any State               | UNPOWERED               | PVIN1 falls below the logic POR threshold                                                                                                                                                                                                                                                          |

| Power                           | INVALID                 | UNPOWERED               | PVIN1 falls below the logic POR threshold. Power cycling is the only way to recover from an internal clock error                                                                                                                                                                                   |

| Reapplication of<br>Logic Power | INVALID                 | RESET                   | VCORE supply recovers its default voltage from a previous short circuit condition                                                                                                                                                                                                                  |

| Shutdown Done                   | ERROR PD                | LOCK                    | The shutdown has been executed                                                                                                                                                                                                                                                                     |

| Auto Rearm                      | FAULT PD                | BIST                    | A shutdown has been executed and the fault counter has not reached its limit. Only allowed if the source of the fault has disappeared.                                                                                                                                                             |

| No Rearm                        | FAULT PD                | LOCK                    | A shutdown has been executed and the fault counter has reached its limit                                                                                                                                                                                                                           |

| Unlock                          | LOCK                    | INIT                    | An unlock has been requested through I <sup>2</sup> C or a restart after TSD or UVLO was permitted. The transition is only permitted if the source of the error has disappeared.<br>NOTE: The IC can also be unlocked by cycling power (from any state, removal of logic power and reapplication). |

#### **Auto Rearm Description**

After a "FAULT", if AutoRearmCnt < AutoRearmCntMax (I<sup>2</sup>C and OTP programmable) NCV92310 restart automatically and goes to the BIST state.

if AutoRearmCnt = AutoRearmCntMax, NCV92310 goes in LOCK mode.  $P_{VIN1}$  has to be removed and applied again to restart the NCV92310. Otherwise a new power-up sequence is started.

See "<u>INTERRUPTION</u>" and "<u>FUNCTIONAL</u> <u>SAFETY</u>" sections to have the FAULT description.

Table 4. AUTO REARM COUNTER

| Bits | AutoRearmCnt_max |

|------|------------------|

| 00   | No restart       |

| 01   | 3                |

| 10   | 15               |

| 11   | 63               |

#### **Bist Retry Description**

BIST error has its own error counter. If BistCnt < BistCnt max, a BIST retry is performed. If BistCnt = BistCntMax ( $I^2C$  and OTP programmable), NCV92310 goes in lock mode.

#### Table 5. BIST COUNTER

| Bits | BistCnt_max |

|------|-------------|

| 0    | No retry    |

| 1    | 1           |

## **Unlock Description**

Once in lock state, NCV92310 regulators are off with INTB and RSTB pins low. Any I<sup>2</sup>C command to start a new power–up sequence or enable one of the regulators will be acknowledged, but power up sequence cannot start if the NCV92310 is locked.

To recover, the NCV92310 must receive one of the following unlock commands.

- Cycling power on PVIN1 pin or

- Set high NLOCK bit or

- In case of TSD having TSD\_REARM bit set high or

- In case of UVLO having UVLO\_REARM bit set high.

After an unlock command, NCV92310 goes in INIT state and reloads the default value of the OTP by resetting all the registers with the exception of the INTERRUPT\_FLAG\_ERR1 and INTERRUPT\_FLAG\_ERR2 registers.

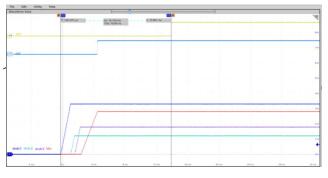

#### Power Up Sequence

All supply rails can be assigned to the power up sequencer. The sequence can be started upon application of power at PVIN1 or through I<sup>2</sup>C. The sequence is preprogrammed through OTP but can be overwritten through I<sup>2</sup>C as well. Once a sequence is started it cannot be interrupted with the exception of the occurrence of a fault or error.

A sequence is built up out of three portions: initialization, the sequence with its slots, and a sequence done wait period. During the initialization it is verified that all assigned rails have no residual voltage on their outputs. A delay can be inserted before starting the first rail, allowing for a delay between the request for a power up sequence and the actual start. The sequence itself consists of slots, and at each slot, one or more power rails can be enabled. A slot is started after the rails of the previous slot are successfully powered up plus an optional delay. The sequence done wait period is added at the end of the sequence and can be used to delay the RSTB signal.

During the initialization phase, the active discharge on the assigned rails is enabled. If, at the end of the initialization phase, one of the assigned supply rails still has a residual voltage on its output, this event is logged and a power up sequence is not started.

A supply is considered enabled when its output voltage is established above the undervoltage detection thresholds of that rail, including its debounce "See <u>VOLTAGE</u> <u>MONITORING</u>" section.

Each rail needs to power up within a timeout period. In case of a timeout, the sequence is considered fault and a shutdown is engaged. The event, and the rail causing this are logged. The device will attempt a new startup sequence if the conditions allow.

Rails can be enabled while operating the device. When enabling, and if that rail is originally assigned to a power up sequence, it is being verified that the rail powers up within the timeout period. Any violation is logged. The violation can be cleared through  $I^2C$ .

The sequence will power up each voltage rail at its default output voltage setting as set through OTP. This default setting can be overwritten through  $I^2C$ .

During the power up sequence, and despite the soft start mechanisms in place, it may be that, during the soft start of DCDC1, the PVIN1 trips the undervoltage lockout detection due to an excessive impedance of the coaxial cable. If DCDC1 is assigned to slot 0 and enabled, and only in this specific case, the device enters a hiccup mode. The power up sequence is aborted so the input supply can recover, and once recovered, the device will continue to soft start DCDC1 repeatedly until the rail is successfully powered up within the timeout period. In all other configurations (DCDC1 assigned to another slot, disabled or another rail assigned to slot 0), this recovery procedure is not supported.

Figure 19. Power-up Sequence State Machine

#### **Table 6. POWER UP SEQUENCER STATES**

| Group  | State             | Туре         | l <sup>2</sup> C | Description                                                                                                                                                                                                                                                                                   |

|--------|-------------------|--------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        | PU INIT           | Transitional | R only           | Only the active discharge on all assigned rails are activated, a timeout is started (64 ms max), the output voltage of the rails are verified with respect to the disable threshold. The state of INTB is frozen and will not change during the power up sequence itself, RSTB is forced low, |

|        | Allow INTB        | Transitional | R only           | The INTB pin is no longer frozen and reflects the actual state of the interrupts, a sequence done wait timer is started                                                                                                                                                                       |

|        | Allow RSTB        | Transitional | R only           | The RSTB pin is released                                                                                                                                                                                                                                                                      |

| SLOT 0 | SLOT 0 INIT       | Transitional | R only           | Upon entry, the slot counter is set to 0, the active discharge of the rails assigned to slot 0 are disabled                                                                                                                                                                                   |