# Automotive Ethernet Transceiver (MAC-PHY) 10BASE-T1S MultiDrop

# **NCV7410**

### Description

The NCV7410 device is an IEEE 802.3cg-compliant Ethernet Transceiver with an integrated Media Access Controller (MAC-PHY).

The NCV7410 can communicate with multiple nodes connected to a shared medium (UTP) at 10 Mbps. It consists of CSMA/CD MAC and PHY with Physical Layer Collision Avoidance (PLCA). PLCA prevents collisions at the physical layer and, therefore, improves the throughput of CSMA/CD. The NCV7410 uses SPI (with a clock up to 25 MHz) as an interface to host MCU.

#### **Features**

- Compliant to IEEE 802.3cg 2019

- Supports Half-Duplex, Multidrop Mode

- Physical Layer Collision Avoidance (PLCA)

- SPI Interface (OPEN Alliance 10BASE-T1x MAC-PHY Serial Interface)

- Distance Measurement between Nodes

- Single 3.3 V Supply Operation

- Transmitter Optimized for Capacitive Coupling to UTP Cable

- MDI Pins Protected against:

- ◆ ±6 kV ESD (HBM, IEC61000-4-2)

- ◆ Transient Pulses (ISO7637)

- Operating Ambient Temperature –40°C to +125°C (T<sub>AMB Class1</sub>)

- Junction Temperature Range -40°C to +150°C

#### **Environment**

• These are Pb-Free Devices

### **Typical Applications**

- Automotive

- Agricultural Machinery

- Machine Control

#### Quality

- Wettable Flank Package for Enhanced Optical Inspection

- NCV Prefix for Automotive and Other Applications Requiring Unique Site and Control Change Requirements; AEC-Q100 Qualified and PPAP Capable

1

#### **MARKING DIAGRAM**

V7410 AWLYYWW

V7410 = Specific Device Code

A = Assembly Location

WL = Wafer Lot YY = Year

WW = Work Week

■ Pb-Free Package

#### ORDERING INFORMATION

See detailed ordering and shipping information on page 64 of this data sheet.

### **TABLE OF CONTENTS**

| Application Information       | . 3 |

|-------------------------------|-----|

| Block Diagram                 |     |

| Pin Assignment                | . 5 |

| Pin Definition                |     |

| Electrical Characteristics    | . 8 |

| SPI Interface Timing          | 10  |

| Detailed Description          | 11  |

| Operating Modes               |     |

| Register Memory Map           | 13  |

| Application Information       |     |

| Device Configuration Examples |     |

### **APPLICATION INFORMATION**

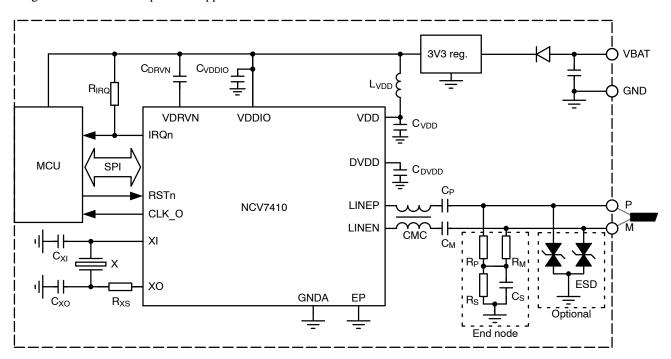

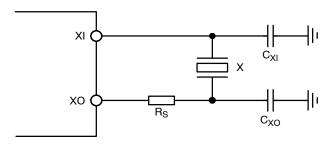

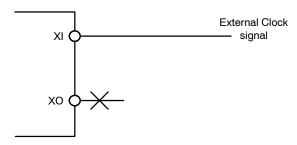

Figure 1 shows an example of an application with the NCV7410.

Figure 1. Basic Application Diagram

Table 1. RECOMMENDED EXTERNAL COMPONENTS FOR THE APPLICATION DIAGRAM

| Component                         | Function                                     | Value                   | Unit | Note                |

|-----------------------------------|----------------------------------------------|-------------------------|------|---------------------|

| C <sub>VDD</sub>                  | Filtering Capacitor, Ceramic                 | 2.2                     | μF   |                     |

| L <sub>VDD</sub>                  | Analog Power Supply Ferrite                  | 1                       | kΩ   | Measured at 100 MHz |

| C <sub>VDDIO</sub>                | Filtering Capacitor, Ceramic                 | 100                     | nF   |                     |

| C <sub>DRVN</sub>                 | Filtering Capacitor, Ceramic                 | 2.2                     | μF   |                     |

| C <sub>DVDD</sub>                 | Filtering Capacitor, Ceramic                 | 2.2                     | μF   |                     |

| R <sub>IRQ</sub>                  | IRQ Pull Up Resistor                         | 10                      | kΩ   |                     |

| Х                                 | Crystal (e.g. Murata XRCGB25M000F3A00R0)     | 25                      | MHz  | ±100 ppm            |

| R <sub>XS</sub>                   | Series Resistor                              | 0                       | Ω    |                     |

| C <sub>XI</sub> , C <sub>XO</sub> | Load Capacitors                              | Depends on used crystal | pF   |                     |

| CMC                               | Common Mode Choke (e.g. TDK ACT1210E-241-2P) | 240                     | μΗ   |                     |

| $C_{P_i}C_M$                      | DC-blocking Coupling Capacitors              | 100                     | nF   | <10%, 50 V          |

| R <sub>P</sub> , R <sub>M</sub>   | Terminating Resistors                        | 49.9                    | Ω    | <1%, ≥0.4 W         |

| C <sub>S</sub>                    | Capacitor                                    | 4.7                     | nF   | <10%, 50 V          |

| R <sub>S</sub>                    | Resistor                                     | 100                     | kΩ   | <10%, ≥0.1 W        |

| ESD                               | ESD Protection                               | SZESD9902 / 9901        |      | Optional            |

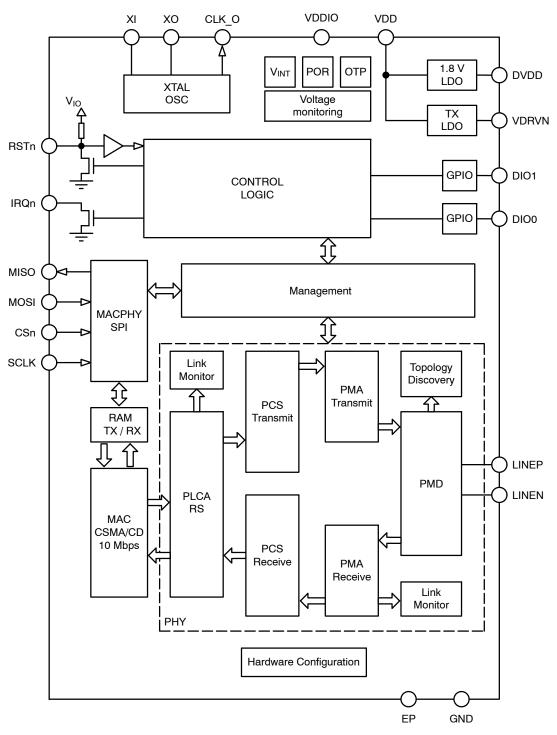

### **BLOCK DIAGRAM**

Figure 2. Block Diagram

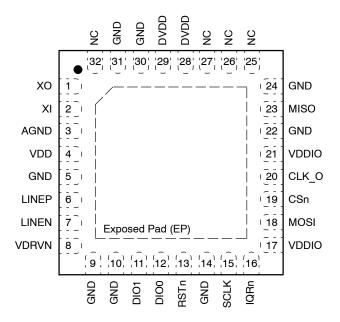

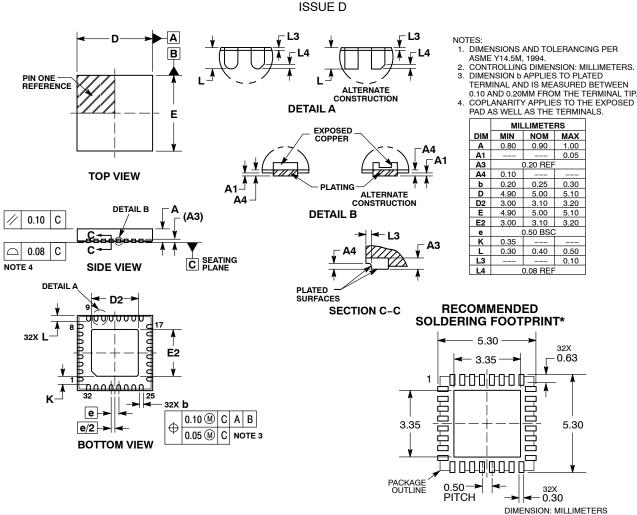

### **PIN ASSIGNMENT**

Figure 3. Pin Assignment - QFN32 (Top View)

# **PIN DEFINITION**

The pinout of the NCV7410 is shown in Figure 3. The pin list is given in Pin Function Description table below.

**Table 2. PIN FUNCTION DESCRIPTION**

| Pin No.                            | Pin Name    | Pin Function               | Description                                                                                                                                                                                                                                             |

|------------------------------------|-------------|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                                  | XO          | Output                     | Crystal XO                                                                                                                                                                                                                                              |

| 2                                  | ΧI          | Input                      | Crystal XI / Reference clock input                                                                                                                                                                                                                      |

| 4                                  | VDD         | Power Supply               | 3.3 V Power Supply Input                                                                                                                                                                                                                                |

| 6                                  | LINEP       | Analog Input / Output      | Positive Medium Dependent Interface (MDI) terminal                                                                                                                                                                                                      |

| 7                                  | LINEN       |                            | Negative Medium Dependent Interface (MDI) terminal                                                                                                                                                                                                      |

| 8                                  | VDRVN       | Supply (regulator output)  | Output of internal TX LDO. Proper decoupling needed.                                                                                                                                                                                                    |

| 11                                 | DIO1        | GPIO                       | General Purpose IO. During BOOT, an internal pull-down is connected                                                                                                                                                                                     |

| 12                                 | DIO0        |                            | to both DIOs. See DIO Configuration Register.                                                                                                                                                                                                           |

| 13                                 | RSTn        | Digital Input, Open Drain  | Reset pin (Active–low), internal 54 k $\Omega$ pull–up, driven low (25 $\Omega$ ) during undervoltage event. To prevent damage, when driving this from an MCU or any active driver, make sure that such drive is configured to be an open drain driver. |

| 15                                 | SCLK        | Digital Input              | SPI interface Shift Clock                                                                                                                                                                                                                               |

| 16                                 | IRQn        | Digital Output, open drain | Interrupt pin, active low                                                                                                                                                                                                                               |

| 17, 21                             | VDDIO       | Supply Input               | Digital I/O voltage reference (3.3 V or 2.5 V)                                                                                                                                                                                                          |

| 18                                 | MOSI        | Digital Input              | SPI interface Serial Data Input                                                                                                                                                                                                                         |

| 19                                 | CSn         |                            | SPI interface Chip Select (active low)                                                                                                                                                                                                                  |

| 20                                 | CLK_O       | Digital Output             | 25 MHz clock output                                                                                                                                                                                                                                     |

| 23                                 | MISO        | Digital Output             | SPI interface Serial Data Output                                                                                                                                                                                                                        |

| 25, 26, 27                         | NC          | Reserved                   | Do not connect                                                                                                                                                                                                                                          |

| 28, 29                             | DVDD        | Supply (regulator output)  | Output of internal 1.8 V LDO. Proper decoupling is needed.                                                                                                                                                                                              |

| 32                                 | NC          | Reserved                   | Do not connect                                                                                                                                                                                                                                          |

| 3, 5, 9, 10, 14,<br>22, 24, 30, 31 | GND         | Ground                     | Connect to GND in the application                                                                                                                                                                                                                       |

| EP                                 | Exposed Pad |                            |                                                                                                                                                                                                                                                         |

**Table 3. MAXIMUM RATINGS**

| Symbol                       | Rating                                                            | Min  | Max         | Unit |

|------------------------------|-------------------------------------------------------------------|------|-------------|------|

| V <sub>VDD_MAX</sub>         | Voltage Supplies (VDD, VDDIO), (Note 1)                           | -0.3 | 3.65        | V    |

| V <sub>DVDD_MAX</sub>        | Low Voltage Supply Output (DVDD)                                  | -0.3 | 1.98        | V    |

| V <sub>LINE_MAX</sub>        | Voltage on LINE Pins                                              | -30  | 30          | V    |

| V <sub>DIGIN_MAX</sub>       | Digital Input Pins                                                | -0.3 | VDDIO + 0.3 | V    |

| V <sub>DIGOUT_MAX</sub>      | Digital Output Pins                                               | -0.3 | VDDIO + 0.3 | V    |

| I <sub>DIGOUT_MAX</sub>      | Current on Digital Output Pins                                    | =    | 20          | mA   |

| V <sub>GND_MAX</sub>         | Ground Pins (GND)                                                 | -0.3 | 0.3         | V    |

| V <sub>TRAN</sub>            | Voltage Transients, Pins LINEP, LINEN per ISO7637 Part 3          | -150 | 100         | V    |

| ESD <sub>System_HBM</sub>    | On Pins LINEP, LINEN (Note 2)                                     | >:   | kV          |      |

| ESD <sub>Component_HBM</sub> | Human Body Model on Pins LINEP, LINEN (Note 3)                    | >:   | kV          |      |

| ESD <sub>Component_HBM</sub> | Human Body Model on All Pins (Note 4)                             | >:   | kV          |      |

| ESD <sub>CDM</sub>           | Charge device Model on All Pins as per JESD22-C101 / AEC-Q100-011 | >±   | V           |      |

| LU                           | Static Latch-up Measured on All Pins per EIA/JESD78 -100 100      |      |             |      |

| T <sub>STG</sub>             | Storage Temperature                                               | 150  | °C          |      |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

1. Refer to ELECTRICAL CHARACTERISTICS, RECOMMENDED OPERATING RANGES and/or APPLICATION INFORMATION for Safe

- Operating parameters.

As per IEC 61000-4-2, 330 Ω / 150 pF

Stressed towards GND as per JESD22-A114 / AEC-Q100-002, 1500 Ω / 100 pF

- 4. As per JESD22-A114 / AEC-Q100-002

### **Table 4. RECOMMENDED OPERATING RANGES**

| Symbol           | Rating                                | Min  | Max   | Unit |

|------------------|---------------------------------------|------|-------|------|

| VDD              | Voltage Supply at VDDA and VDD        | 2.97 | 3.63  | V    |

| VDDIO            | Voltage Supply (VDDIO) for Digital IO | 2.25 | 3.63  | V    |

| DigIO            | DC Voltage at Digital Pins            | 0    | VDDIO | V    |

| T <sub>AMB</sub> | Ambient Temperature                   | -40  | 125   | °C   |

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

### **ELECTRICAL CHARACTERISTICS**

**ELECTRICAL CHARACTERISTICS** (VDD = 2.97 V to 3.63 V; VDDIO = 2.25 V to 3.63 V;  $C_{VDD}$ ,  $C_{VDDA}$ ,  $C_{DRVN}$  = 2.2  $\mu$ F;  $C_{VDDIO}$  = 100 nF;  $T_J$  = -40 to +150°C; for typical values  $T_J$  = 25°C; for min/max values.  $T_J$  = -40 to 150°C; unless otherwise noted. All voltages are referenced to GND (Exposed Pad). Positive currents flow into the respective pin.)

| Symbol                 | Parameter                                                                            | Test Condition                                                           | Min                                                         | Тур       | Max                               | Unit  |

|------------------------|--------------------------------------------------------------------------------------|--------------------------------------------------------------------------|-------------------------------------------------------------|-----------|-----------------------------------|-------|

| POWER SU               | PPLY – PIN VDD                                                                       |                                                                          | •                                                           |           |                                   |       |

| I <sub>VDD</sub>       | Supply Current                                                                       | Transmitting                                                             | _                                                           | 45        | 55                                | mA    |

|                        |                                                                                      | Receiving                                                                | -                                                           | 20        | _                                 | mA    |

|                        |                                                                                      | Standby                                                                  | -                                                           | 13        | -                                 | mA    |

| $V_{uvd\_VDD}$         | Undervoltage Detection Threshold                                                     | VDD falling                                                              | 2.42                                                        | -         | -                                 | V     |

| $V_{uvr\_VDD}$         | Undervoltage Recovery Threshold                                                      | VDD rising                                                               | _                                                           | -         | 2.89                              | V     |

|                        | Undervoltage Threshold Hysteresis                                                    |                                                                          | 95                                                          | 100       | 121                               | mV    |

|                        | Undervoltage Deglitch Time                                                           |                                                                          | 4                                                           | 7         | 15                                | μs    |

| POWER SU               | PPLY – PIN VDDIO                                                                     |                                                                          |                                                             |           |                                   |       |

| I <sub>VDDIO</sub>     | Supply Current                                                                       | Transmitting                                                             | _                                                           | 2         | 4                                 | mA    |

|                        |                                                                                      | Receiving                                                                | _                                                           | 2         | 4                                 | mA    |

|                        |                                                                                      | Standby                                                                  | -                                                           | 2         | 4                                 | mA    |

| V <sub>uvd_VDD</sub>   | Undervoltage Detection Threshold                                                     | VDDIO falling                                                            | 1.83                                                        | -         | _                                 | V     |

| V <sub>uvr_VDD</sub>   | Undervoltage Recovery Threshold                                                      | VDDIO rising                                                             | _                                                           | -         | 2.17                              | V     |

|                        | Undervoltage Threshold Hysteresis                                                    |                                                                          | 70                                                          | 80        | 90                                | mV    |

|                        | Undervoltage Deglitch Time                                                           |                                                                          | 5                                                           | 10        | 20                                | μS    |

| PMA ELECT              | FRICAL MEASUREMENTS - MDI / BUS LINES                                                |                                                                          | •                                                           | •         | -                                 | -     |

| TX <sub>DROOP</sub>    | Transmitter Output Droop (Test Mode 2)                                               | 100 *  V <sub>DROOP</sub> / V <sub>PK</sub>                              | -                                                           | -         | +30                               | %     |

| t <sub>TJ</sub>        | Transmitter Timing Jitter – Symbol-to-Symbol                                         | Test mode 1                                                              | -                                                           | -         | 5                                 | ns    |

| V <sub>PD</sub>        | Transmitter Distortion (Test mode 4)                                                 |                                                                          | -                                                           | -         | 15                                | mV    |

| P <sub>PSD</sub>       | Transmitter Power Spectral Density at Frequency                                      | 0.3 MHz ≤ f < 5 MHz                                                      | Max61                                                       |           |                                   | dBm/H |

|                        | f (MHz)<br>(Test Mode 3)                                                             | 5 MHz ≤ f < 10 MHz                                                       | M                                                           | Z         |                                   |       |

|                        |                                                                                      | 10 MHz ≤ f < 15 MHz                                                      | Min47 - 2f<br>Max61                                         |           |                                   |       |

|                        |                                                                                      | 15 MHz ≤ f ≤ 25 MHz                                                      | Max40 - 1.4f                                                |           |                                   |       |

|                        |                                                                                      | 25 MHz ≤ f ≤ 40 MHz                                                      |                                                             | Max75     |                                   |       |

| f <sub>TR</sub>        | Symbol Transmission Rate                                                             |                                                                          | -                                                           | 12.5      | -                                 | MBd   |

| f <sub>TR_Tol</sub>    | Symbol Transmission Rate Tolerance                                                   |                                                                          | -100                                                        | -         | 100                               | ppm   |

| a <sub>RL_Sdd11</sub>  | MDI Return Loss at Frequency f (MHz) – Applicable                                    | 0.3 MHz ≤ f ≤ 10 MHz                                                     | 14                                                          | -         | -                                 | dB    |

|                        | for Point-to-Point Link Segment                                                      | 10 MHz ≤ f ≤ 40 MHz                                                      | Min. 14                                                     | – 10 × lo | $g_{10}\left(\frac{f}{10}\right)$ | dB    |

| a <sub>LCL_Sdc11</sub> | MDI Mode Conversion Loss at Frequency f (MHz) –                                      | 0.3 MHz ≤ f ≤ 20 MHz                                                     | 43                                                          | _         | -                                 | dB    |

|                        | Applicable for Point-to-Point Link Segment                                           | 20 MHz ≤ f ≤ 200 MHz                                                     | Min. $43 - 20 \times \log_{10} \left( \frac{f}{20} \right)$ |           |                                   | dB    |

| BER                    | Receiver Bit Error Rate                                                              |                                                                          | -                                                           | -         | 10 <sup>-10</sup>                 | _     |

| BER_ACNR               | Bit Error Rate under Alien Crosstalk Noise Injection (with Magnitude of –101 dBm/Hz) | Noise source:<br>Gaussian signal generator<br>with a bandwidth of 40 MHz | -                                                           | -         | 10 <sup>-10</sup>                 | -     |

**ELECTRICAL CHARACTERISTICS** (VDD = 2.97 V to 3.63 V; VDDIO = 2.25 V to 3.63 V;  $C_{VDD}$ ,  $C_{VDDA}$ ,  $C_{DRVN}$  = 2.2  $\mu$ F;  $C_{VDDIO}$  = 100 nF;  $T_J$  = -40 to +150°C; for typical values  $T_J$  = 25°C; for min/max values.  $T_J$  = -40 to 150°C; unless otherwise noted. All voltages are referenced to GND (Exposed Pad). Positive currents flow into the respective pin.) (continued)

|                       | · · · /                                                                         |                                             |                 |      |       |      |  |

|-----------------------|---------------------------------------------------------------------------------|---------------------------------------------|-----------------|------|-------|------|--|

| Symbol                | Parameter                                                                       | Test Condition                              | Min             | Тур  | Max   | Unit |  |

| MDI TRANS             | MITTER (VDD = 3.3 V)                                                            |                                             |                 |      |       |      |  |

| V <sub>TRX_DIFF</sub> | Transmitter Peak Differential Output Voltage                                    | $R_{LOAD}$ = 50 $\Omega$ , Default settings | 0.9             | 1.0  | 1.1   | V    |  |

| R <sub>DRIVER</sub>   | Bus Driver Output Resistance                                                    |                                             | 40              | 50   | 63    | Ω    |  |

| MDI RECEIV            | <b>/ER</b> (VDD = 3.3 V)                                                        |                                             |                 |      |       |      |  |

| R <sub>REC_IN</sub>   | Differential Input Resistance                                                   |                                             | 25              | 40   | 60    | kΩ   |  |

| C <sub>REC_IN</sub>   | Differential Input Capacitance                                                  | At 20 MHz                                   |                 | 5.5  | 7.5   | pF   |  |

| V <sub>REC_CM</sub>   | Common Mode Voltage Range                                                       |                                             | -20             | -    | 20    | V    |  |

| V <sub>REC_TH</sub>   | Receiver Threshold                                                              |                                             | -15             | 0    | 15    | mV   |  |

| V <sub>REC_ED</sub>   | Energy Detection Threshold (Default Value, See PHY Configuration 0 Register)    | Def. value, see RX_DT                       | _               | ±250 | _     | mV   |  |

| V <sub>REC_CD</sub>   | Collision Detection Threshold (Default Value, See PHY Configuration 0 Register) | Def. value, see RX_CD                       | -               | ±700 | _     | mV   |  |

| V <sub>REC_ACC</sub>  | Threshold Accuracy                                                              |                                             | -30             | -    | 30    | mV   |  |

| DIGITAL IO            | DIGITAL IO PINS                                                                 |                                             |                 |      |       |      |  |

| V <sub>IL</sub>       | Low-level Input Voltage                                                         | VDDIO = 2.5 V to 3.3 V                      | _               | _    | 0.7   | V    |  |

| V <sub>IH</sub>       | High-level Input Voltage                                                        | ]                                           | 2               | -    | VDDIO | V    |  |

| V <sub>OL</sub>       | Low-level Output Voltage                                                        | ]                                           | _               | -    | 0.45  | V    |  |

| V <sub>OH</sub>       | High-level Output Voltage                                                       |                                             | VDDIO<br>- 0.45 | -    | -     | V    |  |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

### **SPI INTERFACE TIMING**

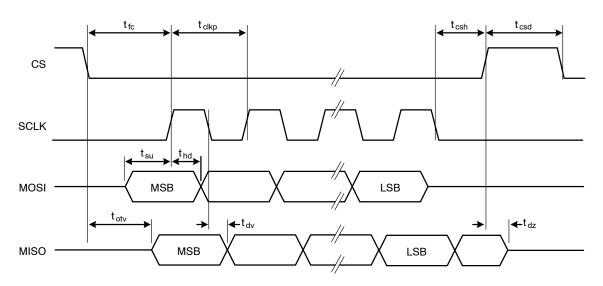

Figure 4. SPI Interface AC Timing Diagram

**Table 5. SPI TIMING CHARACTERISTICS**

| Symbol            | Item                          | Condition             | Min | Тур | Max  | Unit |

|-------------------|-------------------------------|-----------------------|-----|-----|------|------|

| t <sub>clkp</sub> | SPI Clock Period              | VDDIO = 2.5 V ±10%    | 50  | -   | -    | ns   |

|                   |                               | VDDIO = 3.3 V ±10%    | 40  | -   | -    | ns   |

| t <sub>su</sub>   | Data Input Setup Time         | VDDIO = 2.25 – 3.63 V | 8   | -   | -    | ns   |

| t <sub>hd</sub>   | Data Input Hold Time          | VDDIO = 2.25 – 3.63 V | 5   | -   | -    | ns   |

| t <sub>dv</sub>   | Output Data Valid             | VDDIO = 2.5 V ±10%    | -   | -   | 14.5 | ns   |

|                   |                               | VDDIO = 3.3 V ±10%    | -   | -   | 12   | ns   |

| t <sub>otv</sub>  | CS Low to MISO Out Valid      | VDDIO = 2.5 V ±10%    | -   | -   | 14.5 | ns   |

|                   |                               | VDDIO = 3.3 V ±10%    | -   | -   | 12   | ns   |

| t <sub>fc</sub>   | CS Low to Rising Edge of SCLK | VDDIO = 2.25 – 3.63 V | 20  | -   | -    | ns   |

| t <sub>csh</sub>  | SCLK Falling to CS De-assert  | VDDIO = 2.25 – 3.63 V | 5   | -   | 14.5 | ns   |

| t <sub>dz</sub>   | CS De-assert to MISO HIGH-Z   | VDDIO = 2.5 V ±10%    | -   | -   | 14.5 | ns   |

|                   |                               | VDDIO = 3.3 V ±0%     | _   | -   | 12   | ns   |

| t <sub>csd</sub>  | Minimum CS De-assertion Time  | VDDIO = 2.25 – 3.63 V | 350 | -   | _    | ns   |

#### **DETAILED DESCRIPTION**

The NCV7410 is a 10BASE-T1S Physical Layer Transceiver as specified in IEEE 802.3cg with an integrated Media Access Controller (MAC). It supports operation over a shared media (multidrop) network with up to 25 m of a single twisted pair (UTP / STP) connection.

The NCV7410 provides a Serial Peripheral Interface (SPI) in slave mode, allowing low pin count connection to standard, off-the-shelf Microcontrollers or SoC. The NCV7410 provides a link speed of 10 Mbit/s in half-duplex operation.

The MAC-PHY's SPI protocol is compliant to the specification issued by the Open Alliance. The NCV7410 can be locally configured to run Physical Layer Collision Avoidance (PLCA), that supports at least 8 nodes on the shared medium, depending on environmental conditions.

PLCA improves data throughput under high network load and provides additional benefits:

- Nodes are granted transmit opportunities using a round-robin arbitration scheme, enabling fair-shared access to the medium.

- By avoiding multiple back-off and retry events in the embedded MAC, maximum latencies are significantly reduced.

- Protects against the "babbling idiot" problem, as a single station can only transmit when granted an opportunity to do so.

The integration of the PLCA reconciliation sublayer (PLCA RS) in the device enables connected hosts to take full advantage of collision–free Ethernet communication on a single twisted pair, shared medium.

The integrated CSMA/CD 10 Mbps MAC provides the following features:

• Multiple MAC address filtering

- Broadcast / Multicast filtering

- Promiscuous Mode, accepting every frame regardless of its type or address

- FCS generation / checking

- Statistics / Diagnostic Counters

- Status reporting

- Factory provided unique MAC address.

The SPI Protocol handler supports:

- 8-byte, 16-byte, 32-byte and 64-byte data chunks

- Both "Store & Forward" and "Cut-Through" operation

- Protected and Unprotected control transaction

- 4 kB TX-Buffer

- 4 kB RX-Buffer

- SPI clock up to 25 MHz

Additional non-standard features are implemented into the NCV7410:

- Enhanced Noise Immunity PMA operation (ENI)

- Collision detection masking

- PLCA Precedence Mode

- PLCA coordinator selection

- Proprietary topology discovery, allowing to measure the distance between nodes on the link segment works only when all communication partners are onsemi 10BASE-T1S devices: NCV7410, NCV7311, NCN26010 or NCN26000.

The integrated Crystal Oscillator circuitry allows the use of an external CMOS oscillator, a quartz crystal, or any other external clock source, as long as its accuracy is in line with the specifications.

#### **OPERATING MODES**

#### General

The NCV7410 offers two operation modes, that can be selected using strap pin DIO0 during BOOT (reset or power up), NORMAL mode, and ISOLATED mode.

#### **NORMAL Mode**

In NORMAL mode the NCV7410 works as a standard 10BASE-T1S MAC-PHY, connecting to the host via an SPI interface.

#### **ISOLATED Mode**

In ISOLATED mode, LINEP and LINEN pins are held in high impedance mode, SPI interface and DIO pins work as in NORMAL mode.

To move from ISOLATED mode to NORMAL operation, the ISOM bit in the PHY Control Register needs to be cleared.

### **BOOT**

When the RST pin is de-asserted or upon Power ON Reset, the NCV7410 enters BOOT mode. In BOOT mode, all interface pins are either inputs or tri-stated outputs. After the mode pin (DIO0) is sampled, the NCV7410 enters either NORMAL or ISOLATED mode and all interface pins are re-configured accordingly.

The open-drain IRQn pin signals finished boot by a short low pulse (typical duration: 160 ns). If the CS signal is high after the reset, IRQn stays low due to a non-maskable Reset Complete (RESETC) interrupt.

**Table 6. BOOTSTRAPS PIN**

| Pin<br>Name | Bootstrap<br>Function | Description                                                                                             |

|-------------|-----------------------|---------------------------------------------------------------------------------------------------------|

| DIO0        | ISOLATE               | Selects the operation mode: 0 = NORMAL mode 1 = ISOLATED mode Internal Pull-Down connected during BOOT. |

DIO0 can be set to High or Low, using an external device or a pull resistor in the range between 1 k $\Omega$  and 10 k $\Omega$ .

#### **POWER-OFF Mode**

The NCV7410 remains in POWER-OFF mode as long as the voltage at any supply pin (VDD, DVDD, or VDDIO) is below its undervoltage recovery threshold. POWER-OFF mode is also entered from any other operating mode in case of undervoltage detection.

As soon as the voltage at all supply pins rises above the undervoltage recovery threshold, POR is issued, all registers are reset to their default values, and the NCV7410 proceeds to BOOT.

### **REGISTER MEMORY MAP**

The NCV7410 provides the registers grouped in memory map selection groups. See the below table for details.

**Table 7. MEMORY MAP SELECTION GROUP**

| MMS | Width | Memory Map Description                                |

|-----|-------|-------------------------------------------------------|

| 0   | 32    | Standard SPI Control and Status, PHY MIIM (Clause 22) |

| 1   | 32    | MAC Registers                                         |

| 2   | 16    | PHY- PCS Registers (IEEE802.3 MMD3)                   |

| 3   | 16    | PHY- PMA/PCS Registers (IEEE802.3 MMD 1)              |

| 4   | 16    | PHY – PCLA and Vendor-specific<br>Registers (MMD 31)  |

The OA-SPI protocol always treats registers as 32-bit. Registers that are 16-bit wide will have the two most significant bytes read as 0x00. For write commands to 16-bit registers, the two most significant bytes are ignored. Each register is defined by a table containing the following attributes:

- MMS: The target MMS that together with ADDR uniquely identifies the register

- Address: The 16-bit target address within the specified MMS at which the register can be accessed

- Default: The initial value of the register after a reset

In the same table, each bit-field is further qualified by the following attributes:

- Bit(s): The bit number/range at which the field is located within the register

- Name: The name of the field

- Description: A short description of the field

- Default: The initial value of the field after a reset

- Access: The allowed access type of the field, as specified in Table 7

# Table 8. DESCRIPTION OF REGISTER FIELD ACCESS TYPES USED IN THIS DOCUMENT

| Access | Memory Map Description                                                                                                |

|--------|-----------------------------------------------------------------------------------------------------------------------|

| RW     | The field can be read from and written to                                                                             |

| RO     | The field is read-only. Writes to a RO field are ignored. If a default value is present, then the field is a constant |

| RO-SCR | Read-only field that self-clears on read.                                                                             |

| R/W1C  | Read-only field that can be cleared by writing a 1 to it.                                                             |

| RW-SC  | Read-Write filed, whose content is cleared to its default values after the underlying operation is completed.         |

| RO-LH  | Read-only, Latch high on the occurrence of the underlying event. Clears on read.                                      |

Table 9. REGISTER MAP OVERVIEW

|          | MS         | MAP OVER   |           |                                                                |

|----------|------------|------------|-----------|----------------------------------------------------------------|

| Hex      | Dec        | Hex        | Dec       | Name                                                           |

| MMS0 REG | ISTERS     |            |           |                                                                |

| 0x0      | 0          | 0x0        | 0         | SPI Identification Register, IDVER                             |

|          |            | 0x1        | 1         | SPI Identification Register, PHY ID                            |

|          |            | 0x2        | 2         | SPI Capabilities, SPICAP                                       |

|          |            | 0x3        | 3         | Reset Control and Status, RESET                                |

|          |            | 0x4        | 4         | SPI Protocol Configuration Register, CONFIG0                   |

|          |            | 0x8        | 8         | SPI Protocol Status Register, STATUS0                          |

|          |            | 0xB        | 11        | Buffer Status Register, BUFSTS                                 |

|          |            | 0xC        | 12        | Interrupt Mask Register, IMASK                                 |

|          |            | 0xFF00     | 65280     | PHY Control Register                                           |

|          |            | 0xFF01     | 65281     | PHY Status Register                                            |

|          |            | 0xFF02     | 65282     | PHY Identifier 0 Registers                                     |

|          |            | 0xFF03     | 65283     | PHY Identifier 1 Registers                                     |

| MMS1 REG | ISTERS - R | EGISTERS F | ELATED TO | THE MAC                                                        |

| 0x1      | 1          | 0x0        | 0         | MAC Control0 Register                                          |

|          |            | 0x10       | 16        | Address Filter 0 Low, ADDRFILT0L                               |

|          |            | 0x11       | 17        | Address Filter 0 High, ADDRFILT0H                              |

|          |            | 0x12       | 18        | Address Filter 1 Low, ADDRFILT1L                               |

|          |            | 0x13       | 19        | Address Filter 1 High, ADDRFILT1H                              |

|          |            | 0x14       | 20        | Address Filter 2 Low, ADDRFILT2L                               |

|          |            | 0x15       | 21        | Address Filter 2 High, ADDRFILT2H                              |

|          |            | 0x16       | 22        | Address Filter 3 Low, ADDRFILT3L                               |

|          |            | 0x17       | 23        | Address Filter 3 High, ADDRFILT3H                              |

|          |            | 0x20       | 32        | Address Mask 0 Low, ADDRMASK0L                                 |

|          |            | 0x21       | 33        | Address Mask 0 High, ADDRMASK0H                                |

|          |            | 0x22       | 34        | Address Mask 1 Low, ADDRMASK1L                                 |

|          |            | 0x23       | 35        | Address Mask 1 High, ADDRMASK1H                                |

|          |            | 0x24       | 36        | Address Mask 2 Low, ADDRMASK2L                                 |

|          |            | 0x25       | 37        | Address Mask 2 High, ADDRMASK0H                                |

|          |            | 0x26       | 38        | Address Mask 3 Low, ADDRMASK3L                                 |

|          |            | 0x27       | 39        | Address Mask 0 High, ADDRMASK3H                                |

|          |            | 0x30       | 48        | Statistic, Sent Bytes Counter Low, STOCTETSTXL                 |

|          |            | 0x31       | 49        | Statistic, Sent Bytes Counter High, STOCTETSTXH                |

|          |            | 0x32       | 50        | Statistic, Frames Sent Ok, STFRAMESTXOK                        |

|          |            | 0x33       | 51        | Statistic, Broadcast Frames Sent Ok, STBCASTTXOK               |

|          |            | 0x34       | 52        | Statistic, Multicast Frames Sent Ok, STMCASTTXOK               |

|          |            | 0x35       | 53        | Statistic, 64-byte Frames Sent Ok, STFRAMESTX64                |

|          |            | 0x36       | 54        | Statistic, 65-byte to 127-byte Frames Sent Ok, STFRAMESTX65    |

|          |            | 0x37       | 55        | Statistic, 128-byte to 255-byte Frames Sent Ok, STFRAMESTX128  |

|          |            | 0x38       | 56        | Statistic, 256-byte to 511-byte Frames Sent Ok, STFRAMESTX256  |

|          |            | 0x39       | 57        | Statistic, 512-byte to 1023-byte Frames Sent Ok, STFRAMESTX512 |

Table 9. REGISTER MAP OVERVIEW (continued)

| M       | IMS         | Add        | ress       |                                                                            |

|---------|-------------|------------|------------|----------------------------------------------------------------------------|

| Hex     | Dec         | Hex        | Dec        | Name                                                                       |

| MMS1 RE | GISTERS – R | EGISTERS F | RELATED TO | THE MAC                                                                    |

| 0x1     | 1           | 0x3A       | 58         | Statistic, 1024-byte or More Frames Sent Ok, STFRAMESTX1024                |

|         |             | 0x3B       | 59         | Statistic, Aborted frames Due to TX-buffer Underflow, STUNDERFLOW          |

|         |             | 0x3C       | 60         | Statistic, Frames Transmitted after a Single Collision, STSINGLECOL        |

|         |             | 0x3D       | 61         | Statistic, Frames Transmitted after Multiple Collisions, STMULITCOL        |

|         |             | 0x3E       | 62         | Statistic, Frames Transmitted after Excessive Collisions, STEXCESSCOL      |

|         |             | 0x3F       | 63         | Statistic, Frames Transmitted after Deferral, STDEFEEREDTX                 |

|         |             | 0x40       | 64         | Statistic, Counter of CRS De-assertion During Frame Transmission, STCRSERR |

|         |             | 0x41       | 65         | Statistic, Received Bytes Counter Low, STOCTETSRXL                         |

|         |             | 0x42       | 66         | Statistic, Received Bytes Counter High, STOCTETSRXH                        |

|         |             | 0x43       | 67         | Statistic, Frames Received Ok, STFRAMESRXOK                                |

|         |             | 0x44       | 68         | Statistic, Broadcast Frames Received Ok, STBCASTRXOK                       |

|         |             | 0x45       | 69         | Statistic, Multicast Frames Received Ok, STMCASTRXOK                       |

|         |             | 0x46       | 70         | Statistic, 64-byte Frames Received Ok, STFRAMESRX64                        |

|         |             | 0x47       | 71         | Statistic, 65-byte to 127-byte Frames Received Ok, STFRAMESTX65            |

|         |             | 0x48       | 72         | Statistic, 128-byte to 255-byte Frames Received Ok, STFRAMESTX128          |

|         |             | 0x49       | 73         | Statistic, 256-byte to 511-byte Frames Received Ok, STFRAMESTX256          |

|         |             | 0x4A       | 74         | Statistic, 512-byte to 1023-byte Frames Received Ok, STFRAMESTX512         |

|         |             | 0x4B       | 75         | Statistic, 1024-byte or More Frames Received Ok, STFRAMESTX1024            |

|         |             | 0x4C       | 76         | Statistic, Dropped Too Short Frames, STRUNTERR                             |

|         |             | 0x4D       | 77         | Statistic, Dropped Too Long Frames STRXTOOLONG                             |

|         |             | 0x4E       | 78         | Statistic, Dropped FCS Error Frames STFCSERRS                              |

|         |             | 0x4F       | 79         | Statistic, Symbol Errors During Frame Reception, STSYMBOLERRS              |

|         |             | 0x50       | 80         | Statistic, Align Errors During Frame Reception, STALIGNERRS                |

|         |             | 0x51       | 81         | Statistic, RX Buffer Overflow Errors, STRXOVERFLOW                         |

|         |             | 0x52       | 82         | Statistic, RX Dropped Frame Count, STRXDROPPED                             |

| IMS2 RE | GISTERS – R | EGISTERS F | RELATED TO | THE PHY: PCS                                                               |

| 0x2     | 2           | 0x5        | 5          | Devices in Package 1 Register                                              |

|         |             | 0x6        | 6          | Devices in Package 2 Register                                              |

|         |             | 0x8F3      | 2291       | 10BASE-T1S PCS Control Register                                            |

|         |             | 0x8F4      | 2292       | 10BASE-T1S PCS Status Register                                             |

|         |             | 0x8F5      | 2293       | 10BASE-T1S PCS Diagnostics Register 1                                      |

|         |             | 0x8F6      | 2294       | 10BASE-T1S PCS Diagnostics Register 2                                      |

| IMS3 RE | GISTERS – R | EGISTERS F | RELATED TO | THE PHY: PMA                                                               |

| 0x3     | 3           | 0x5        | 5          | Devices in Package 1 Register                                              |

|         |             | 0x6        | 6          | Devices in Package 2 Register                                              |

|         |             | 0x12       | 18         | BASE-T1 Extended Ability Register                                          |

|         |             | 0x8F9      | 2297       | 10BASE-T1S PMA Control Register                                            |

|         |             | 0x8FA      | 2298       | 10BASE-T1S PMA Status Register                                             |

|         |             | 0x8FB      | 2299       | 10BASE-T1S Test Mode Control Register                                      |

Table 9. REGISTER MAP OVERVIEW (continued)

| М        | MS          | Add         | ress       |                                                         |

|----------|-------------|-------------|------------|---------------------------------------------------------|

| Hex      | Dec         | Hex         | Dec        | Name                                                    |

| MMS4 REC | GISTERS - F | REGISTERS F | RELATED TO | THE PHY: PLCA                                           |

| 0x4      | 4           | 0x8000      | 32768      | Chip Revision Register                                  |

|          |             | 0x8001      | 32769      | PHY Configuration 1 Register                            |

|          |             | 0x8002      | 32770      | PLCA Extensions Register                                |

|          |             | 0x8003      | 32771      | PMA Tune 0 Register                                     |

|          |             | 0x8004      | 32772      | PMA Tune 1 Register                                     |

|          |             | 0xCA00      | 51712      | PLCA Register Map and Identification Register, PLCIDVER |

|          |             | 0xCA01      | 51713      | PCLA Control 0 Register, PLCACTRL0                      |

|          |             | 0xCA02      | 51714      | PCLA Control 1 Register, PLCACTRL1                      |

|          |             | 0xCA03      | 51715      | PCLA Status Register, PLCASTATUS                        |

|          |             | 0xCA04      | 51716      | PCLA Transmit Opportunity Timer Register, PLCATOTMR     |

|          |             | 0xCA05      | 51717      | PCLA Burst Mode Register, PLCABURST                     |

| MMS12 RE | GISTERS -   | VENDOR SP   | ECIFIC REG | ISTERS                                                  |

| 0xC      | 12          | 0x10        | 16         | MIIM Interrupt Control Register                         |

|          |             | 0x11        | 17         | MIIM Interrupt Status Register                          |

|          |             | 0x12        | 18         | DIO Configuration Register                              |

|          |             | 0x16        | 22         | Topology Discovery Control Register                     |

|          |             | 0x17        | 23         | Topology Discovery Status Register                      |

|          |             | 0x18        | 24         | Topology Discovery Result Register                      |

|          |             | 0x19        | 25         | Topology Discovery Precision Register                   |

|          |             | 0x1A        | 26         | Topology Reference Counter Timer Register               |

|          |             | 0x1001      | 4097       | PHY Configuration 0 Register                            |

|          |             | 0x1002      | 4098       | MACID0                                                  |

|          |             | 0x1003      | 4099       | MACID1                                                  |

|          |             | 0x1004      | 4100       | Chip Info Register                                      |

|          |             | 0x1005      | 4101       | NVM Health Register                                     |

### **MMS0 REGISTERS**

### SPI Identification Register, IDVER

MMS: 0 Address: 0x0 Default: 0x11

| Bit(s) | Name   | Description          | Default | Access |

|--------|--------|----------------------|---------|--------|

| 31:8   | -      | Value always 0       | 0x0     | RO     |

| 7:4    | MAJVER | Major Version Number | 0x1     | RO     |

| 3:0    | MINVER | Minor Version Number | 0x1     | RO     |

# SPI Identification Register, PHY ID

MMS: 0 Address: 0x1 Default: –

| Bit(s) | Name  | Description                                                                                                                                                                                             | Default | Access |

|--------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--------|

| 31:10  | OUI   | Organizational Unique Identifier                                                                                                                                                                        | -       | RO     |

|        |       | Records the 22 MSBs of the OUI in reverse order. Bit 31 maps bit 2 of the OUI, bit 10 maps bit 23 of the OUI. Bits 0 and 1 are 0.  NOTE: onsemi's OUIs can be found at: https://standards-oui.ieee.org/ |         |        |

| 9:4    | MODEL | Model Number                                                                                                                                                                                            | 0x1A    | RO     |

| 3:0    | REV   | Chip Revision Number                                                                                                                                                                                    | 0x1     | RO     |

### **SPI Capabilities, SPICAP**

MMS: 0 Address: 0x2 Default: 0x5A3

| Bit(s) | Name    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Default | Access |

|--------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--------|

| 31:11  | =       | Value always 0                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0x0     | RO     |

| 10     | TXFCSVC | TX Frame Check Sequence Verification  NCV7410 MAC supports checking the FCS on outgoing frames when not configured to compute and append the FCS to TX frames. When this feature is enabled and the MAC-PHY is operating in "store & forward" mode, frames from the SPI having an incorrect checksum are not forwarded to the line. If the MAC-PHY is operating in "cut-through" mode, incorrect frames are aborted in such a way the receiving nodes discard them. | 0x1     | RO     |

| 9      | IPARC   | Indirect PHY Register Access Not supported by NCV7410                                                                                                                                                                                                                                                                                                                                                                                                               | 0x0     | RO     |

| 8      | DPRAC   | Direct PHY Register Access Capability NCV7410's PHY registers are accessed using direct access through SPI control instructions.                                                                                                                                                                                                                                                                                                                                    | 0x1     | RO     |

| 7      | СТС     | Cut-through Capability NCV7410 can operate in Cut-through-Mode                                                                                                                                                                                                                                                                                                                                                                                                      | 0x1     | RO     |

| 6      | FTC     | Frame Timestamp Capability NCV7410 does not provide Frame Timestamping functionality                                                                                                                                                                                                                                                                                                                                                                                | 0x0     | RO     |

| 5      | AIDC    | Address Increment Disable Capability  The SPI protocol implemented into NCV7410 supports disabling the address auto-increment during control transactions, allowing the host to perform repeated read/write access to the same register.                                                                                                                                                                                                                            | 0x1     | RO     |

| 4      | SEQ     | TX Data Chunk Sequence and Retry Not supported by NCV7410                                                                                                                                                                                                                                                                                                                                                                                                           | 0x0     | RO     |

| 3      | _       | Value always 0                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0x0     | RO     |

| 2:0    | MINCPS  | Minimum Supported Chunk Payload Size NCV7410 supports 8-byte minimum payload size. See OA-SPI specification section 9.2.3.9 for details.                                                                                                                                                                                                                                                                                                                            | 0x3     | RO     |

### Reset Control and Status, RESET

MMS: 0 Address: 0x3 Default: 0x0

| Bit | (s) | Name  | Description                                                                                                                          | Default | Access |

|-----|-----|-------|--------------------------------------------------------------------------------------------------------------------------------------|---------|--------|

| 31  | :1  | -     | Value always 0                                                                                                                       | 0x0     | RO     |

| С   | )   | RESET | Soft Reset Writing a 1 into this bit initiated a MAC and PHY reset to their initial state. Reset starts after CS pin is de-asserted. | 0       | RW-SC  |

# SPI Protocol Configuration Register, CONFIG0

MMS: 0 Address: 0x4 Default: 0x6

| Bit(s) | Name      | Description                                                                                                                                                                                                                                                                 | Default | Access |

|--------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--------|

| 31:16  | -         | Value always 0                                                                                                                                                                                                                                                              | 0x0     | RO     |

| 15     | SYNC      | Configuration Synchronization  When set to 0, NCV7410 does not accept TX or RX frames, as its configuration may not be complete. Once the host completes the configuration of NCV7410 it should set this bit to 1. Once set, the bit can only be cleared by a system reset. | 0x0     | RW-1   |

| 14     | TXFCSVE   | Transmit Frame Check Sequence Validation Enable  When set, the final 4 octets of all Ethernet frames conveyed via SPI are validated as an Ethernet FCS. When using this option, the FCSA bit in the MACCTRL0 shall be cleared.                                              | 0x0     | RW     |

| 13     | CSARFE    | CS Align Receive Frame Enable  When set, all received Ethernet frames start at the beginning of the receive chunk following the CSn assertion with a Start Word Offset of zero. When this bit is cleared, received frames may begin anywhere within the chunk payload.      | 0x0     | RW     |

| 12     | ZARFE     | Zero Align Receive Frame Enable  When set, all received Ethernet frames start at the beginning of the received chunk with a Start Word Offset of zero. When this bit is cleared, received frames may begin anywhere within the chunk payload.                               | 0x0     | RW     |

| 11:10  | TXCTHRESH | Transmit Credit Threshold  Configures the minimum number of transmit credits (TXC) that have to be available for asserting IRQn, after TXC went down to zero.  00 ≥ 1 credit (the default) 01 ≥ 4 credits 10 ≥ 8 credits 11 ≥ 16 credits                                    | 0x0     | RW     |

| 9      | TXCTE     | Transmit Cut Though Enable  When set to one, this bit enables sending frames in cut-through mode to reduce the average TX latency.                                                                                                                                          | 0x0     | RW     |

| 8      | RXCTE     | Receive Cut-through Enable  When set to one, this bit enables receiving frames in cut-through mode to reduce the average RX latency.                                                                                                                                        | 0x0     | RW     |

| 7      | FTSE      | Frame Timestamp Enable This feature is not supported by NCV7410. The bit is read-only                                                                                                                                                                                       | 0x0     | RO     |

| 6      | FTSS      | Receive Frame Timestamp Select This feature is not supported by NCV7410. The bit is read-only                                                                                                                                                                               | 0x0     | RO     |

| 5      | PROTE     | Enable Control Data Read/Write Protection Refer to OA–SPI specification section 7.4 for details                                                                                                                                                                             | 0x0     | RW     |

| 4:3    | -         | Value always 0                                                                                                                                                                                                                                                              | 0x0     | RO     |

| 2:0    | CPS       | Chunk Payload Size  0x3 Chunk Payload size is 8 bytes  0x4 Chunk Payload size is 16 bytes  0x5 Chunk Payload size is 32 bytes  0x6 Chunk Payload site is 64 bytes (default)                                                                                                 | 0x6     | RW     |

# SPI Protocol Status Register, STATUS0

MMS: 0 Address: 0x8 Default: 0x40

| Bit(s) | Name   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Default | Access |

|--------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--------|

| 31:13  | -      | Value always 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0x0     | RO     |

| 12     | CDPE   | Control Data Protection Error  When configured to control data read/write protection (set bit PORTE of CONFIGO Register), this bit indicates that the MAC-PHY has detected an error in the last control transaction.                                                                                                                                                                                                                                                                                                                                     | 0       | R/W1C  |

| 11     | TXFCSE | Transmit Frame Check Sequence Error  When set, this bit indicates that the MAC-PHY has detected that the outgoing frame's FCS added by the host is invalid. To clear this bit, write a "1" to this field.                                                                                                                                                                                                                                                                                                                                                | 0       | R/W1C  |

| 10     | TTSCAC | Always 0. Time stamping is not implemented into NCV7410                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 0       | RO     |

| 9      | TTSCAB |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0       | RO     |

| 8      | TTSCAA |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0       | RO     |

| 7      | PHYINT | PHY Interrupt When 1, the embedded PHY is generating an interrupt request. This bit can only be cleared when the interrupt event of the PHY is acknowledged. See MIIM Interrupt Control Register.                                                                                                                                                                                                                                                                                                                                                        | 0       | RO     |

| 6      | RESETC | Reset Complete  This bit is set when the reset procedure is completed and the device is ready to be configured. When set, it will generate a non-maskable interrupt on IRQn to notify the SPI host that the reset has completed. In addition, when this bit is set, the EXST bit in the RX footer is also set. To clear this bit, the host shall write a 1 to it.                                                                                                                                                                                        | 1       | R/W1C  |

| 5      | HDRE   | Header Error Indicates that a header error occurred since this bit was last cleared. When set, the MAC-PHY has detected an invalid header received from the SPI host due to a parity check error.                                                                                                                                                                                                                                                                                                                                                        | 0       | R/W1C  |

| 4      | LOFE   | Loss of Framing Error  When 1, this bit indicates that the NCV7410 has detected a de-assertion of CS prior to the expected end of a data chunk or a command control transaction, resulting in loss of data.                                                                                                                                                                                                                                                                                                                                              | 0       | R/W1C  |

| 3      | RXBOE  | Receive Buffer Overflow Error  When 1, this bit indicates that a frame coming from the network was discarded due to the receive buffer being full.                                                                                                                                                                                                                                                                                                                                                                                                       | 0       | R/W1C  |

| 2      | TXBUE  | Transmit Buffer Underflow Error  When 1, this bit indicates that the transmit buffer experienced an underflow condition and the transmitted frame was lost. This situation can only happen when the NCV7410 is configured to operate in TX cut-through mode.                                                                                                                                                                                                                                                                                             | 0       | R/W1C  |

| 1      | TXBOE  | Transmit Buffer Overflow Error  When 1 this bit indicates that the transmit buffer overflowed and that the transmit frame data was lost.                                                                                                                                                                                                                                                                                                                                                                                                                 | 0       | R/W1C  |