# onsemi

## High Voltage, Half Bridge Driver NCP5104, NCV5104

The NCP5104 is a High Voltage Power gate Driver providing two outputs for direct drive of 2 N-channel power MOSFETs or IGBTs arranged in a half-bridge configuration. It uses the bootstrap technique to insure a proper drive of the High-side power switch.

#### Features

- High Voltage Range: up to 600 V

- dV/dt Immunity ±50 V/nsec

- Gate Drive Supply Range from 10 V to 20 V

- High and Low Drive Outputs

- Output Source / Sink Current Capability 250 mA / 500 mA

- 3.3 V and 5 V Input Logic Compatible

- Up to V<sub>CC</sub> Swing on Input Pins

- Extended Allowable Negative Bridge Pin Voltage Swing to -10 V for Signal Propagation

- Matched Propagation Delays between Both Channels

- 1 Input with Internal Fixed Dead Time (520 ns)

- Under V<sub>CC</sub> LockOut (UVLO) for Both Channels

- Pin to Pin Compatible with Industry Standards

- NCV Prefix for Automotive and Other Applications Requiring Unique Site and Control Change Requirements; AEC-Q100 Qualified and PPAP Capable

- These Devices are Pb–Free, Halogen Free/BFR Free and are RoHS Compliant

#### **Typical Applications**

• Half-Bridge Power Converters

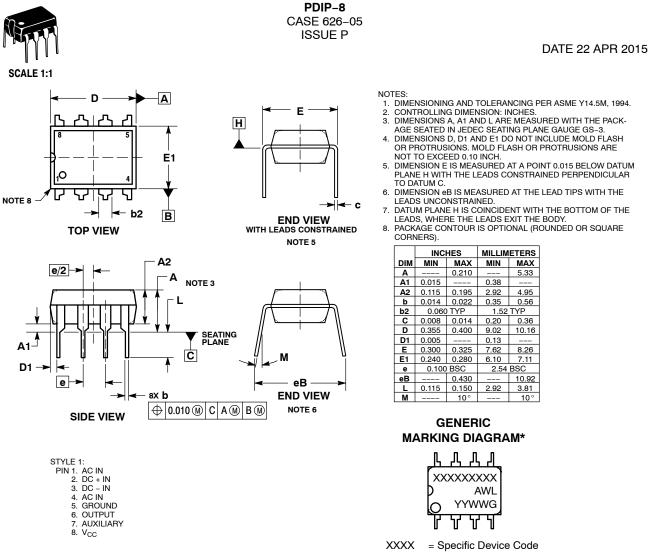

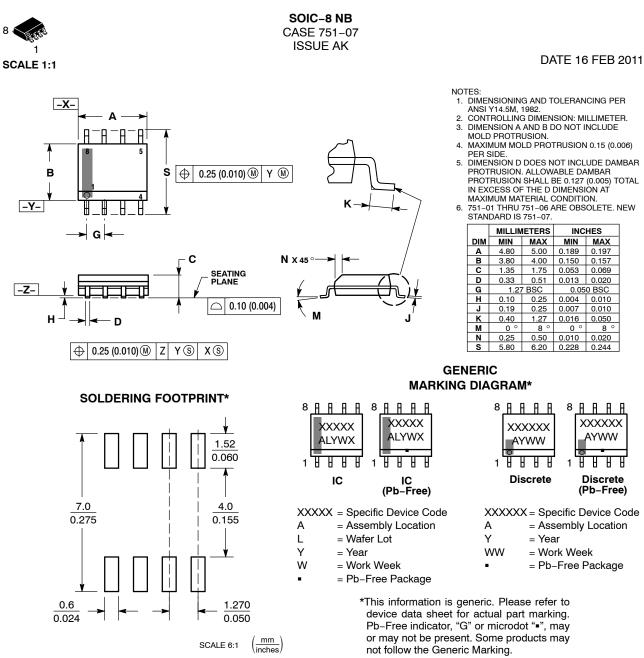

SOIC-8 D SUFFIX CASE 751

PDIP-8 P SUFFIX CASE 626

#### MARKING DIAGRAM

| = Specific Device Code |

|------------------------|

| = Assembly Location    |

| = Wafer Lot            |

| = Year                 |

| = Work Week            |

| = Pb-Free Package      |

|                        |

#### PINOUT INFORMATION

| _                | - |   |    |        |

|------------------|---|---|----|--------|

| vcc 🗝            | 1 | 8 |    | VBOOT  |

| IN III<br>SD III | 2 | 7 |    | DRV_HI |

| SD 🚥             | 3 | 6 |    | BRIDGE |

| GND 📼            | 4 | 5 | ╞╍ | DRV_LO |

| _                |   |   |    | _      |

8 Pin Package

#### **ORDERING INFORMATION**

| Device      | Package             | Shipping <sup>†</sup> |

|-------------|---------------------|-----------------------|

| NCP5104DR2G | SOIC-8<br>(Pb-Free) | 2500 /<br>Tape & Reel |

| NCV5104DR2G | SOIC-8<br>(Pb-Free) | 2500 /<br>Tape & Reel |

#### DISCONTINUED (Note 1)

| NCP5104PG PDIP-8 50 Units/Ra<br>(Pb-Free) |

|-------------------------------------------|

|-------------------------------------------|

†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, <u>BRD8011/D.</u>

1. **DISCONTINUED:** This device is not recommended for new design. Please contact your **onsemi** representative for information. The most current information on this device may be available on <u>www.onsemi.com</u>.

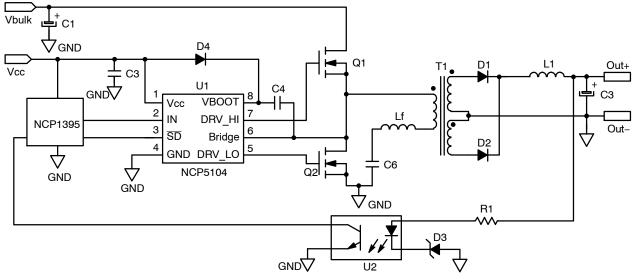

Figure 1. Typical Application Resonant Converter (LLC type)

Figure 2. Typical Application Half Bridge Converter

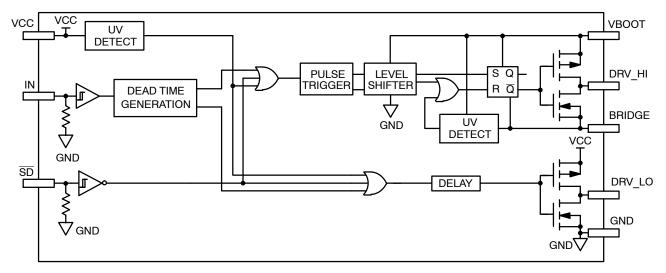

#### Figure 3. Detailed Block Diagram

#### PIN DESCRIPTION

| Pin Name          | Description                                          |

|-------------------|------------------------------------------------------|

| V <sub>CC</sub>   | Low Side and Main Power Supply                       |

| IN                | Logic Input                                          |

| SD                | Logic Input for Shutdown                             |

| GND               | Ground                                               |

| DRV_LO            | Low Side Gate Drive Output                           |

| V <sub>BOOT</sub> | Bootstrap Power Supply                               |

| DRV_HI            | High Side Gate Drive Output                          |

| BRIDGE            | Bootstrap Return or High Side Floating Supply Return |

#### MAXIMUM RATINGS

| Rating                                 | Symbol                                                                                                                                    | Value                                                   | Unit    |

|----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|---------|

| V <sub>CC</sub>                        | Main power supply voltage                                                                                                                 | -0.3 to 20                                              | V       |

| V <sub>CC_transient</sub>              | Main transient power supply voltage:<br>IV <sub>CC_max</sub> = 5 mA during 10 ms                                                          | 23                                                      | V       |

| V <sub>BOOT</sub>                      | VHV: High Voltage BOOT Pin                                                                                                                | -1 to 620                                               | V       |

| V <sub>BRIDGE</sub>                    | VHV: High Voltage BRIDGE pin                                                                                                              | -1 to 600                                               | V       |

| V <sub>BRIDGE</sub>                    | Allowable Negative Bridge Pin Voltage for IN_LO Signal Propagation to DRV_LO (see characterization curves for detailed results)           | -10                                                     | V       |

| V <sub>BOOT-</sub> V <sub>BRIDGE</sub> | VHV: Floating supply voltage                                                                                                              | -0.3 to 20                                              | V       |

| V <sub>DRV_HI</sub>                    | VHV: High side output voltage                                                                                                             | V <sub>BRIDGE</sub> – 0.3 to<br>V <sub>BOOT</sub> + 0.3 | V       |

| V <sub>DRV_LO</sub>                    | Low side output voltage                                                                                                                   | –0.3 to V <sub>CC</sub> + 0.3                           | V       |

| dV <sub>BRIDGE</sub> /dt               | Allowable output slew rate                                                                                                                | 50                                                      | V/ns    |

| $V_{\rm IN}, V_{\rm SD}$               | Inputs IN & SD                                                                                                                            | -1.0 to V <sub>CC</sub> + 0.3                           | V       |

|                                        | ESD Capability:<br>– HBM model (all pins except pins 6–7–8 in 8)<br>– Machine model (all pins except pins 6–7–8)                          | 2<br>200                                                | kV<br>V |

|                                        | Latch up capability per JEDEC JESD78                                                                                                      |                                                         |         |

| R <sub>θJA</sub>                       | Power dissipation and Thermal characteristics<br>PDIP-8: Thermal Resistance, Junction-to-Air<br>SO-8: Thermal Resistance, Junction-to-Air | 100<br>178                                              | °C/W    |

| T <sub>ST</sub>                        | Storage Temperature Range                                                                                                                 | -55 to +150                                             | °C      |

| T <sub>J_max</sub>                     | Maximum Operating Junction Temperature                                                                                                    | +150                                                    | °C      |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

#### ELECTRICAL CHARACTERISTIC (V<sub>CC</sub> = V<sub>boot</sub> = 15 V, V<sub>GND</sub> = V<sub>bridge</sub>, -40°C < T<sub>J</sub> < 125°C, Outputs loaded with 1 nF)

|                                                                                                           |                        | T <sub>J</sub> −40°C to 125°C |     | 5°C |       |

|-----------------------------------------------------------------------------------------------------------|------------------------|-------------------------------|-----|-----|-------|

| Rating                                                                                                    | Symbol                 | Min                           | Тур | Max | Units |

| OUTPUT SECTION                                                                                            | •                      |                               |     |     |       |

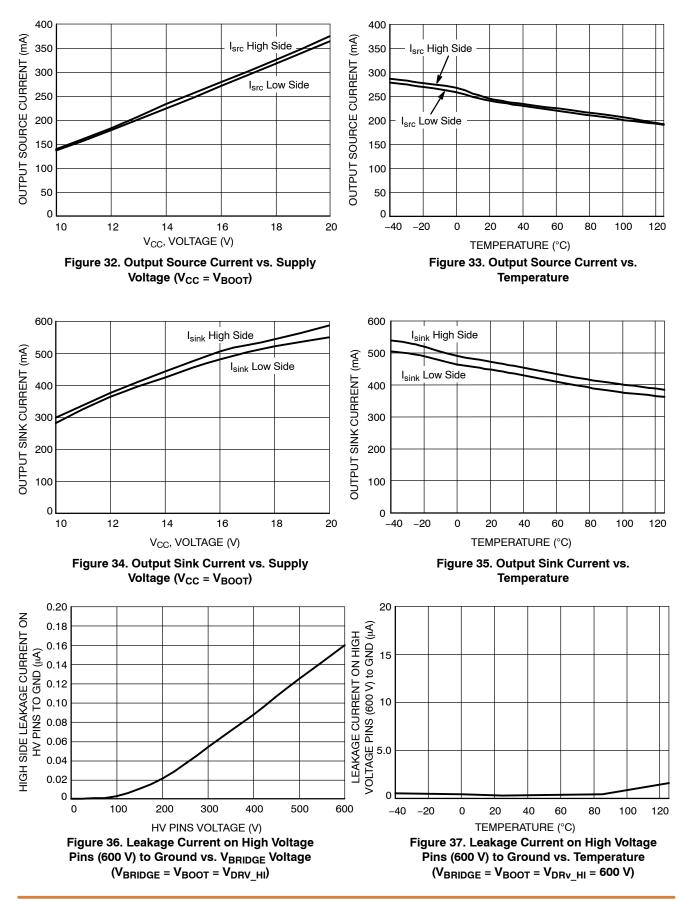

| Output high short circuit pulsed current V <sub>DRV</sub> = 0 V, PW $\leq$ 10 $\mu$ s (Note 2)            | I <sub>DRVsource</sub> | -                             | 250 | -   | mA    |

| Output low short circuit pulsed current V <sub>DRV</sub> = Vcc, PW $\leq$ 10 $\mu$ s (Note 2)             | I <sub>DRVsink</sub>   | -                             | 500 | -   | mA    |

| Output resistor (Typical value @ 25°C) Source                                                             | R <sub>OH</sub>        | -                             | 30  | 60  | Ω     |

| Output resistor (Typical value @ 25°C) Sink                                                               | R <sub>OL</sub>        | -                             | 10  | 20  | Ω     |

| High level output voltage, V <sub>BIAS</sub> -V <sub>DRV_XX</sub> @ I <sub>DRV_XX</sub> = 20 mA           | V <sub>DRV_H</sub>     | _                             | 0.7 | 1.6 | V     |

| Low level output voltage V <sub>DRV_XX</sub> @ I <sub>DRV_XX</sub> = 20 mA                                | V <sub>DRV_L</sub>     | -                             | 0.2 | 0.6 | V     |

| DYNAMIC OUTPUT SECTION                                                                                    |                        |                               |     |     |       |

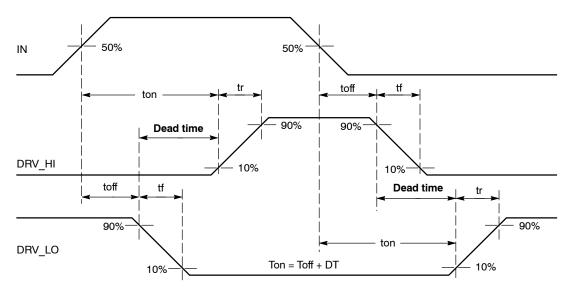

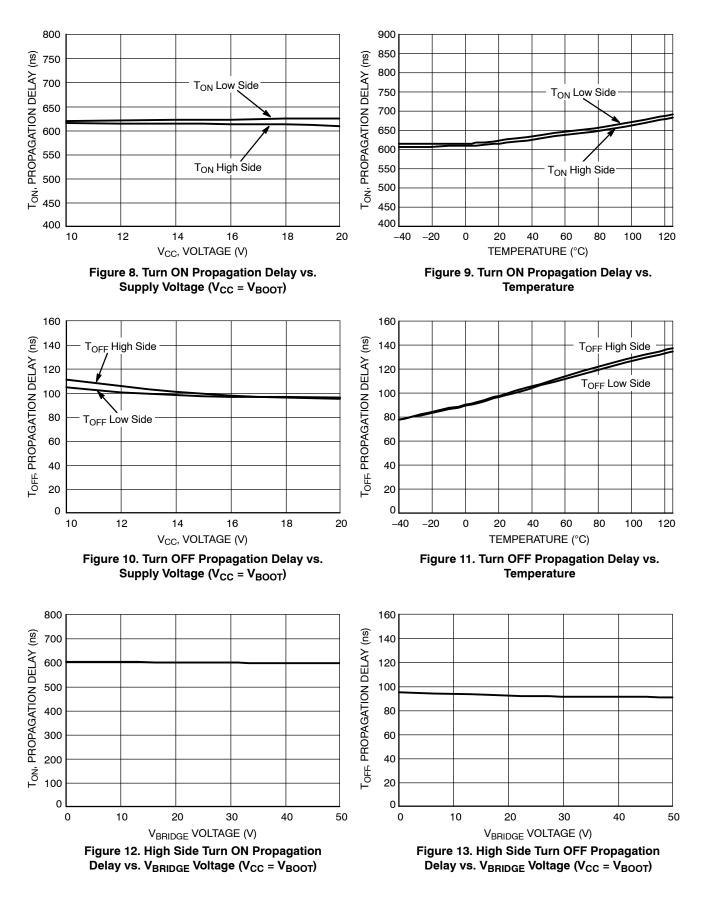

| Turn-on propagation delay (Vbridge = 0 V) (Note 3)                                                        | t <sub>ON</sub>        | -                             | 620 | 800 | ns    |

| Turn-off propagation delay (Vbridge = 0 V or 50 V) (Note 4)                                               | t <sub>OFF</sub>       | -                             | 100 | 170 | ns    |

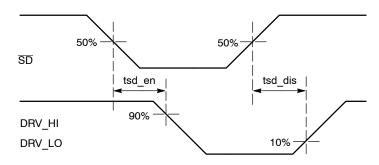

| Shutdown propagation delay, when Shutdown is enabled                                                      | t <sub>sd_en</sub>     | _                             | 100 | 170 | ns    |

| Shutdown propagation delay, when Shutdown is disabled                                                     | t <sub>sd_dis</sub>    | -                             | 620 | 800 | ns    |

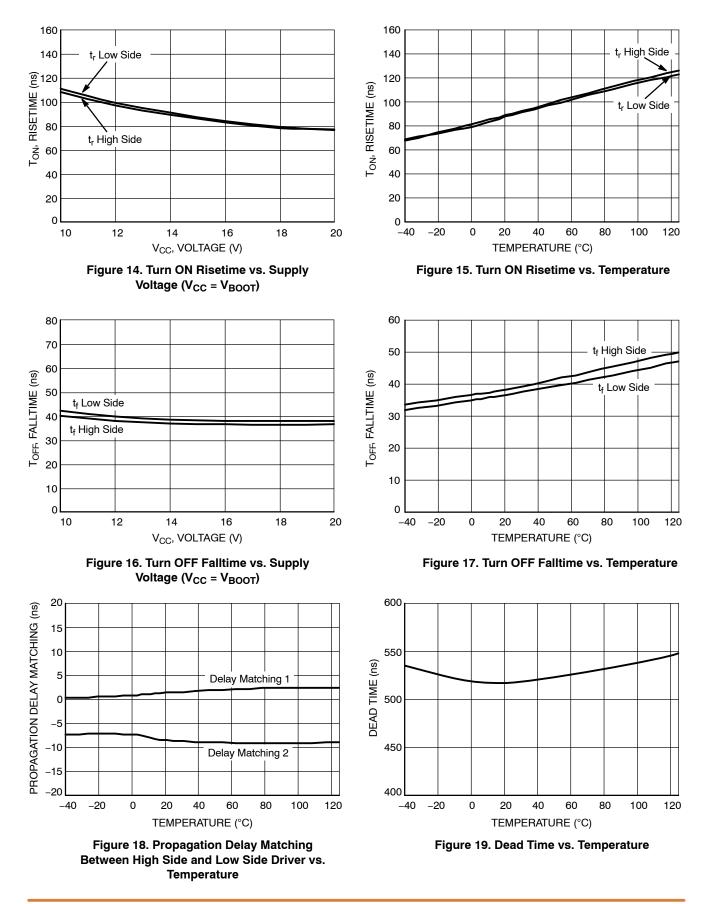

| Output voltage rise time (from 10% to 90% @ V <sub>CC</sub> = 15 V) with 1 nF load                        | t <sub>r</sub>         | _                             | 85  | 160 | ns    |

| Output voltage fall time (from 90% to 10% @ $V_{CC}$ = 15 V) with 1 nF load                               | t <sub>f</sub>         | -                             | 35  | 75  | ns    |

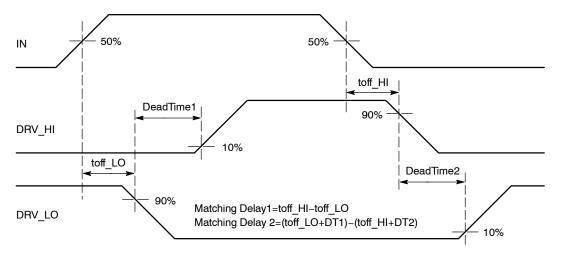

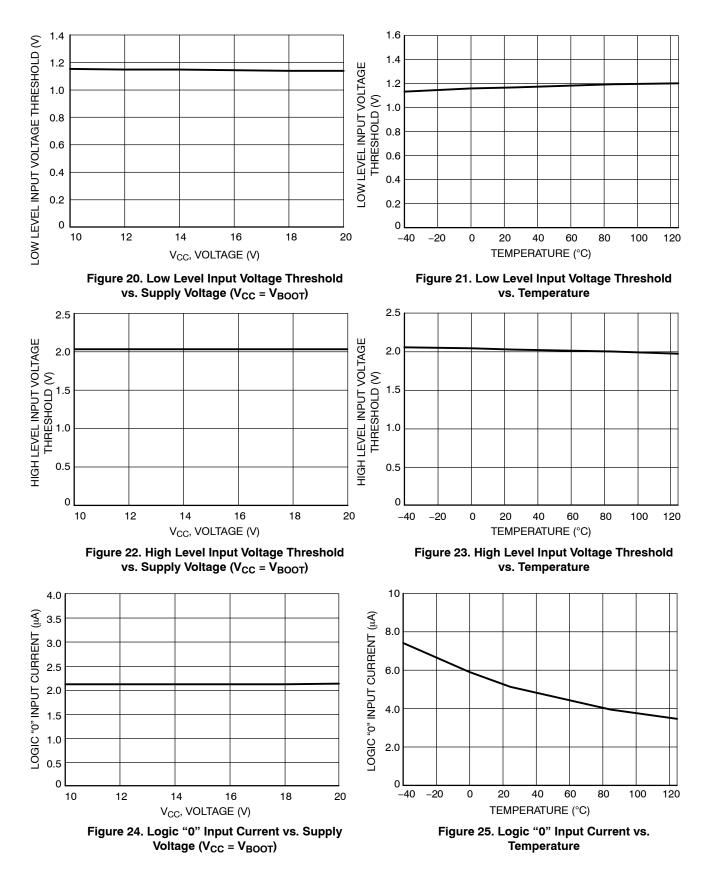

| Propagation delay matching between the High side and the Low side<br>@ 25°C (Note 5)                      | Δt                     | -                             | 10  | 45  | ns    |

| nternal fixed dead time (Note 6)                                                                          | DT                     | 400                           | 520 | 650 | ns    |

| INPUT SECTION                                                                                             | •                      |                               |     |     |       |

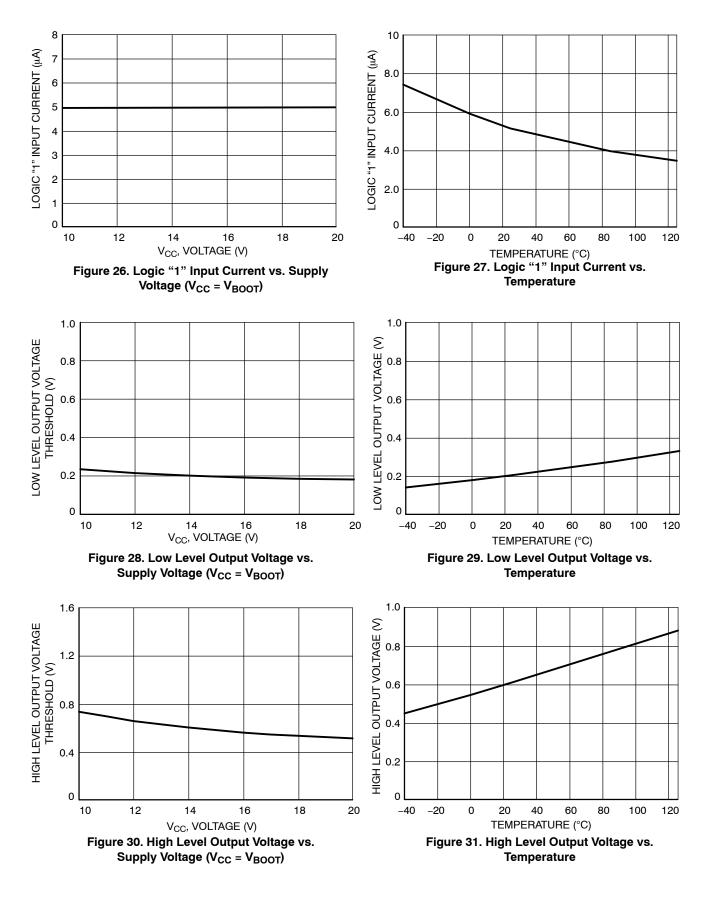

| Low level input voltage threshold                                                                         | V <sub>IN</sub>        | -                             | -   | 0.8 | V     |

| nput pull–down resistor (V <sub>IN</sub> < 0.5 V)                                                         | R <sub>IN</sub>        | _                             | 200 | -   | kΩ    |

| High level input voltage threshold                                                                        | V <sub>IN</sub>        | 2.3                           | -   | -   | V     |

| Logic "1" input bias current @ V <sub>IN</sub> = 5 V @ 25°C                                               | I <sub>IN+</sub>       | _                             | 5   | 25  | μΑ    |

| Logic "0" input bias current @ V <sub>IN</sub> = 0 V @ 25°C                                               | I <sub>IN-</sub>       | _                             | -   | 2.0 | μA    |

| SUPPLY SECTION                                                                                            |                        |                               | •   |     |       |

| Vcc UV Start-up voltage threshold                                                                         | Vcc_stup               | 8.0                           | 8.9 | 9.8 | V     |

| /cc UV Shut-down voltage threshold                                                                        | Vcc_shtdwn             | 7.3                           | 8.2 | 9.0 | V     |

| Hysteresis on Vcc                                                                                         | Vcc_hyst               | 0.3                           | 0.7 | -   | V     |

| Vboot Start-up voltage threshold reference to bridge pin<br>(Vboot_stup = Vboot - Vbridge)                | Vboot_stup             | 8.0                           | 8.9 | 9.8 | V     |

| Vboot UV Shut-down voltage threshold                                                                      | Vboot_shtdwn           | 7.3                           | 8.2 | 9.0 | V     |

| Hysteresis on Vboot                                                                                       | Vboot_shtdwn           | 0.3                           | 0.7 | -   | V     |

| Leakage current on high voltage pins to GND<br>(V <sub>BOOT</sub> = V <sub>BRIDGE</sub> = DRV_HI = 600 V) | I <sub>HV_LEAK</sub>   | -                             | 5   | 40  | μΑ    |

| Consumption in active mode (Vcc = Vboot, fsw = 100 kHz and 1 nF load on poth driver outputs)              | ICC1                   | -                             | 4   | 5   | mA    |

| Consumption in inhibition mode (Vcc = Vboot)                                                              | ICC2                   | _                             | 250 | 400 | μA    |

| Vcc current consumption in inhibition mode                                                                | ICC3                   | _                             | 200 | -   | μA    |

| Vboot current consumption in inhibition mode                                                              | ICC4                   |                               | 50  | _   | μA    |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions. 2. Parameter guaranteed by design.

Parameter guaranteed by design.

T<sub>ON</sub> = T<sub>OFF</sub> + DT

Turn-off propagation delay @ Vbridge = 600 V is guaranteed by design.

See characterization curve for ∆t parameters variation on the full range temperature.

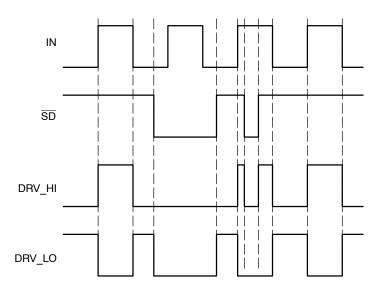

Timing diagram definition see: Figure 4, Figure 5 and Figure 6.

Figure 4. Input/Output Timing Diagram

Note: DRV\_HI output is in phase with the input

Figure 5. Timing Definitions

Figure 6. Matching Propagation Delay Definition

Figure 7. Shutdown Waveform Definition

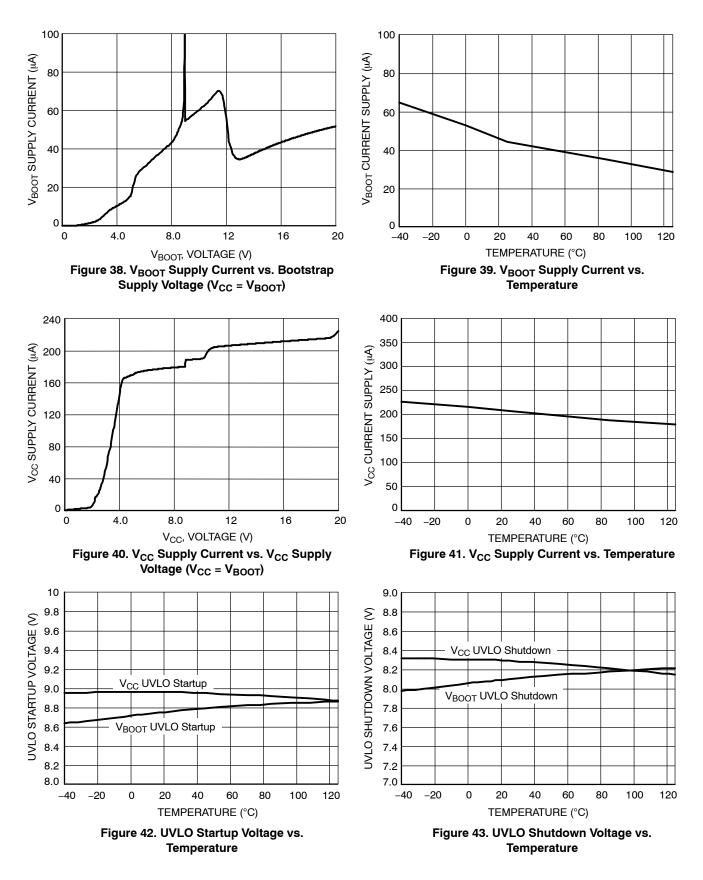

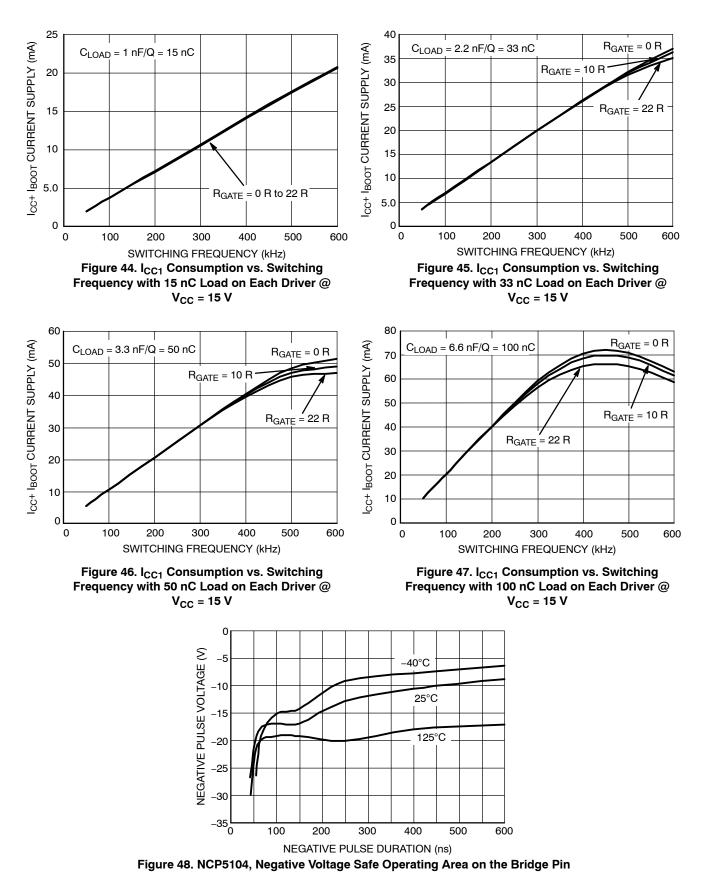

#### **CHARACTERIZATION CURVES**

www.onsemi.com 13

## onsemi

A = Assembly Location

- WL = Wafer Lot

- YY = Year

- WW = Work Week

- G = Pb–Free Package

\*This information is generic. Please refer to device data sheet for actual part marking. Pb-Free indicator, "G" or microdot "•", may or may not be present. Some products may not follow the Generic Marking.

| DOCUMENT NUMBER:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 98ASB42420B | Electronic versions are uncontrolled except when accessed directly from the Document Repository.<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|--|

| DESCRIPTION:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | PDIP-8      |                                                                                                                                                                                     | PAGE 1 OF 1 |  |  |

| onsemi and ONSEMi are trademarks of Semiconductor Components Industries, LLC dba onsemi or its subsidiaries in the United States and/or other countries. onsemi reserves the right to make changes without further notice to any products herein. onsemi makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. onsemi does not convey any license under its patent rights or others. |             |                                                                                                                                                                                     |             |  |  |

© Semiconductor Components Industries, LLC, 2019

## onsemi

\*For additional information on our Pb-Free strategy and soldering details, please download the **onsemi** Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

#### STYLES ON PAGE 2

| DOCUMENT NUMBER:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 98ASB42564B Electronic versions are uncontrolled except when accessed directly from the Document Repository<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |  |             |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|-------------|--|--|

| DESCRIPTION:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | SOIC-8 NB                                                                                                                                                                                      |  | PAGE 1 OF 2 |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                |  |             |  |  |

| onsemi and ONSEMI are trademarks of Semiconductor Components Industries, LLC dba onsemi or its subsidiaries in the United States and/or other countries. onsemi reserves the right to make changes without further notice to any products herein. onsemi makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. onsemi does not convey any license under its patent rights or the rights of others. |                                                                                                                                                                                                |  |             |  |  |

#### SOIC-8 NB CASE 751-07 ISSUE AK

STYLE 1: PIN 1. EMITTER COLLECTOR 2. COLLECTOR 3. 4. EMITTER 5. EMITTER BASE 6. 7 BASE EMITTER 8. STYLE 5: PIN 1. DRAIN 2. DRAIN З. DRAIN DRAIN 4. GATE 5. 6. GATE SOURCE 7. 8. SOURCE STYLE 9: PIN 1. EMITTER, COMMON COLLECTOR, DIE #1 COLLECTOR, DIE #2 2. З. EMITTER, COMMON 4. 5. EMITTER, COMMON 6 BASE. DIE #2 BASE, DIE #1 7. 8. EMITTER, COMMON STYLE 13: PIN 1. N.C. 2. SOURCE 3 GATE 4. 5. DRAIN 6. DRAIN DRAIN 7. 8. DRAIN STYLE 17: PIN 1. VCC 2. V2OUT V10UT З. TXE 4. 5. RXE 6. VFF 7. GND 8. ACC STYLE 21: PIN 1. CATHODE 1 2. CATHODE 2 3 CATHODE 3 CATHODE 4 4. 5. CATHODE 5 6. COMMON ANODE COMMON ANODE 7. 8. CATHODE 6 STYLE 25: PIN 1. VIN 2 N/C REXT З. 4. GND 5. IOUT 6. IOUT IOUT 7. 8. IOUT STYLE 29: BASE, DIE #1 PIN 1. 2 EMITTER, #1 BASE, #2 З. EMITTER, #2 4. 5 COLLECTOR, #2 COLLECTOR, #2 6.

STYLE 2: PIN 1. COLLECTOR, DIE, #1 2. COLLECTOR, #1 COLLECTOR, #2 3. 4 COLLECTOR, #2 BASE, #2 5. EMITTER, #2 6. 7 BASE #1 EMITTER, #1 8. STYLE 6: PIN 1. SOURCE 2. DRAIN 3. DRAIN SOURCE 4. SOURCE 5. 6. GATE GATE 7. 8. SOURCE STYLE 10: GROUND PIN 1. BIAS 1 OUTPUT 2. З. GROUND 4. 5. GROUND 6 BIAS 2 INPUT 7. 8. GROUND STYLE 14: PIN 1. N-SOURCE 2. N-GATE 3 P-SOURCE P-GATE 4. P-DRAIN 5 6. P-DRAIN N-DRAIN 7. N-DRAIN 8. STYLE 18: PIN 1. ANODE ANODE 2. SOURCE 3. GATE 4. 5. DRAIN 6 DRAIN CATHODE 7. 8. CATHODE STYLE 22: PIN 1. I/O LINE 1 2. COMMON CATHODE/VCC 3 COMMON CATHODE/VCC 4. I/O LINE 3 COMMON ANODE/GND 5. 6. I/O LINE 4 7. I/O LINE 5 8. COMMON ANODE/GND STYLE 26: PIN 1. GND 2 dv/dt З. ENABLE 4. ILIMIT 5. SOURCE SOURCE 6. SOURCE 7. 8. VCC STYLE 30: DRAIN 1 PIN 1. DRAIN 1 2 GATE 2 З. SOURCE 2 4. SOURCE 1/DRAIN 2 SOURCE 1/DRAIN 2 5. 6.

STYLE 3: PIN 1. DRAIN, DIE #1 DRAIN, #1 2. DRAIN, #2 З. DRAIN, #2 4. GATE, #2 5. SOURCE, #2 6. 7 GATE #1 8. SOURCE, #1 STYLE 7: PIN 1. INPUT 2. EXTERNAL BYPASS THIRD STAGE SOURCE GROUND З. 4. 5. DRAIN 6. GATE 3 SECOND STAGE Vd 7. FIRST STAGE Vd 8. STYLE 11: PIN 1. SOURCE 1 GATE 1 SOURCE 2 2. 3. GATE 2 4. 5. DRAIN 2 6. DRAIN 2 DRAIN 1 7. 8. DRAIN 1 STYLE 15: PIN 1. ANODE 1 2. ANODE 1 ANODE 1 3 ANODE 1 4. 5. CATHODE, COMMON CATHODE, COMMON CATHODE, COMMON 6. 7. CATHODE, COMMON 8. STYLE 19: PIN 1. SOURCE 1 GATE 1 SOURCE 2 2. 3. GATE 2 4. 5. DRAIN 2 6. MIRROR 2 7. DRAIN 1 8. **MIRROR 1** STYLE 23: PIN 1. LINE 1 IN COMMON ANODE/GND COMMON ANODE/GND 2. 3 LINE 2 IN 4. LINE 2 OUT 5. COMMON ANODE/GND COMMON ANODE/GND 6. 7. 8. LINE 1 OUT STYLE 27: PIN 1. ILIMIT 2 OVI 0 UVLO З. 4. INPUT+ 5. 6. SOURCE SOURCE SOURCE 7. 8 DRAIN

#### STYLE 4: PIN 1. 2. ANODE ANODE ANODE З. 4. ANODE ANODE 5. 6. ANODE 7 ANODE COMMON CATHODE 8. STYLE 8: PIN 1. COLLECTOR, DIE #1 2. BASE, #1 BASE #2 З. COLLECTOR, #2 4. COLLECTOR, #2 5. 6. EMITTER, #2 EMITTER, #1 7. 8. COLLECTOR, #1 STYLE 12: PIN 1. SOURCE SOURCE 2. 3. GATE 4. 5. DRAIN 6. DRAIN DRAIN 7. 8. DRAIN STYLE 16 EMITTER, DIE #1 PIN 1. 2. BASE, DIE #1 EMITTER, DIE #2 3 BASE, DIE #2 4. 5. COLLECTOR, DIE #2 6. COLLECTOR, DIE #2 COLLECTOR, DIE #1 7. COLLECTOR, DIE #1 8. STYLE 20: PIN 1. SOURCE (N) GATE (N) SOURCE (P) 2. 3. 4. GATE (P) 5. DRAIN 6. DRAIN DRAIN 7. 8. DRAIN STYLE 24: PIN 1. BASE EMITTER 2. 3 COLLECTOR/ANODE COLLECTOR/ANODE 4. 5. CATHODE

6. CATHODE COLLECTOR/ANODE 7. 8. COLLECTOR/ANODE STYLE 28: PIN 1. SW\_TO\_GND 2. DASIC OFF DASIC\_SW\_DET З. 4. GND 5. 6. V MON VBULK 7. VBULK

7. VOULK 8. VIN

| DOCUMENT NUMBER: | 98ASB42564B | Electronic versions are uncontrolled except when accessed directly from the Document Repository.<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |

|------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|

| DESCRIPTION:     | SOIC-8 NB   |                                                                                                                                                                                     | PAGE 2 OF 2 |  |

|                  |             |                                                                                                                                                                                     |             |  |

SOURCE 1/DRAIN 2

7.

8. GATE 1

onsemi and ONSEMI are trademarks of Semiconductor Components Industries, LLC dba onsemi or its subsidiaries in the United States and/or other countries. onsemi reserves the right to make changes without further notice to any products herein. onsemi makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. onsemi does not convey any license under its patent rights or others.

7.

8

COLLECTOR, #1

COLLECTOR, #1

onsemi, ONSEMI, and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <u>www.onsemi.com/site/pdf/Patent\_Marking.pdf</u>. onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or indental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi does not convey any license under any of its intellectual property rights nor the rights of others. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification. Buyer shall indemnify and hold onsemi and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs,

#### ADDITIONAL INFORMATION

TECHNICAL PUBLICATIONS:

Technical Library: www.onsemi.com/design/resources/technical-documentation onsemi Website: www.onsemi.com

ONLINE SUPPORT: <u>www.onsemi.com/support</u> For additional information, please contact your local Sales Representative at <u>www.onsemi.com/support/sales</u>