# JN Semiconductor®

To kara more about Old Semiconductor, please visit our website at

Please note. As part of the Fairchild Semiconductor integration, some of the Fairchild orderable part numbers will need to change in order to meet ON Semiconductor's system requirements. Since the ON Semiconductor product management systems do not have the ability to manage part nomenclature that utilizes an underscore (\_), the underscore (\_) in the Fairchild part numbers will be changed to a dash (-). This document may contain device numbers with an underscore (\_). Please check the ON Semiconductor website to verify the updated device numbers. The most current and up-to-date ordering information can be found at <a href="www.onsemi.com">www.onsemi.com</a>. Please email any questions regarding the system integration to Fairchild <a href="guestions@onsemi.com">questions@onsemi.com</a>.

ON Semiconductor and the ON Semiconductor logo are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any EDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officer

May 2024

# **FAN7621B PFM Controller for Half-Bridge Resonant Converters**

#### **Features**

- Variable Frequency Control with 50% Duty Cycle for Half-bridge Resonant Converter Topology

- High Efficiency through Zero Voltage Switching (ZVS)

- Fixed Dead Time (350ns)

- Up to 300kHz Operating Frequency

- Pulse Skipping for Frequency Limit (Programmable) at Light-Load Condition

- Remote On/Off Control using CON Pin

- Protection Functions: Over-Voltage Protection (OVP), Overload Protection (OLP), Over-Current Protection (OCP), Abnormal Over-Current Prote Joi (AOCP), Internal Thermal Shutdown (TSD)

#### **Applications**

- PDP and LCD TVs

- Desktop PCs and Ser

- Adapters

- Telecom Po

- Video Gan Co

#### **Description**

The FAN7621B is a pulse fr ency modulation controller for high-efficiency nalt-, dge resonant converters. Offering everything necess by to build a reliable and robust reso ant con rter he FAN7621B simplifies designs at im loves oductivity, while improving perform. ce. a FAN 621B includes a highside gate-dri e circ a. a arate current controlled oscillator free ency it c.cuit, soft-start, and built-in protection incomes. To high-side gate-drive circuit has non ode use cancellation capability, which able operation with excellent noise iar, tec Using the zero-voltage-switching (ZVS) ii huri tec liqu dramatically reduces the switching losses and efficincy is significantly improved. The ZVS also reduces (ne switching ic se noticeably, which allows a small-pized Electromagnetic Interference (EMI) filter.

The FAN76212 can be applied to various resonant converter topologies; such as series resonant, parallel rescriant, and LLC resonant converters.

#### Related Resources

Half-bridge LLC Resonant Converter Design series Fairchild Power Switch ( $\mathsf{FPS}^\mathsf{TM}$ )

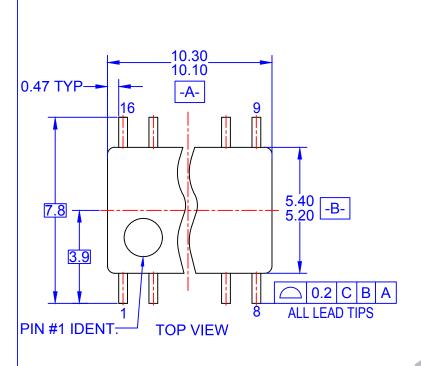

### .g Information

| Part Number | Operating Junction Temperature | Package                             | Packaging<br>Method |

|-------------|--------------------------------|-------------------------------------|---------------------|

| FAN7621BSJ  | -40°C ~ 130°C                  | 16-Lead Small Outline Package (SOP) | Tube                |

| FAN7621BSJX | -40°C ~ 130°C                  | 10-Lead Small Oddille Package (SOP) | Tape & Reel         |

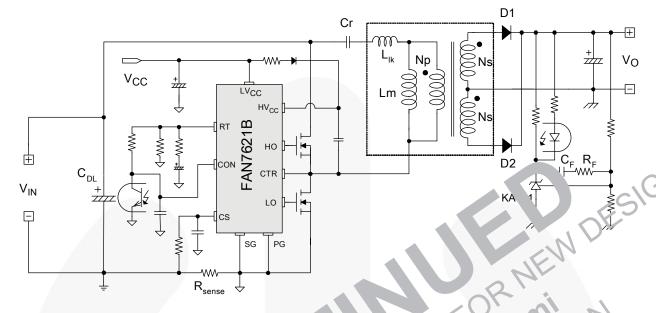

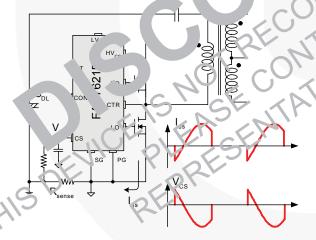

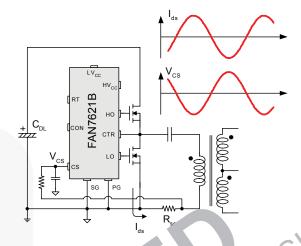

# **Application Circuit Diagram**

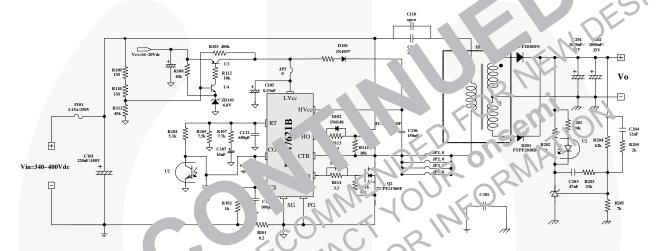

Figure 1. Typical Application Cir (LLC 'es ant Half-Bridge Convertor)

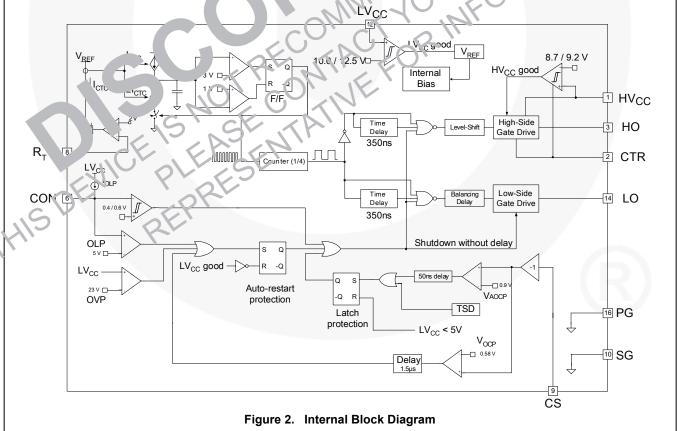

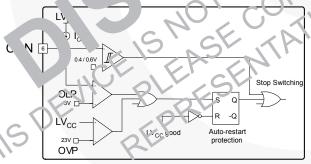

## **Block Diagram**

© 2009 Fairchild Semiconductor Corporation FAN7621B •

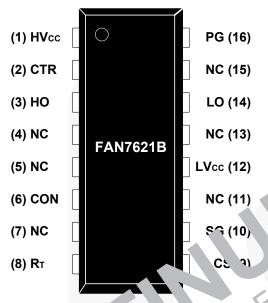

# **Pin Configuration**

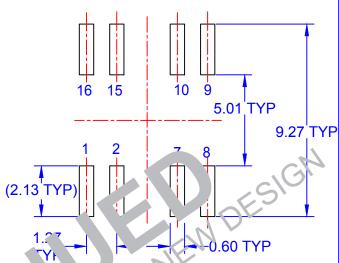

ckage liag m Figure 3

#### **Pin Definitions**

|     |        |                  | (4) NC                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

|-----|--------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|     |        |                  | (6) CON NC (11)                                                                                                                                                                                                                                                                                                         |  |  |  |  |

|     |        |                  | (6) CON [                                                                                                                                                                                                                                                                                                               |  |  |  |  |

|     |        |                  | (8) R <sub>T</sub> Ct 2)                                                                                                                                                                                                                                                                                                |  |  |  |  |

| Pir | n Defi | nitions          | Figure 3 vckage Viag vm                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| Р   | Pin #  | Name             | Description                                                                                                                                                                                                                                                                                                             |  |  |  |  |

|     | 1      | HV <sub>cc</sub> | This is to supply oltage of the high-side gate-drive circuit IC.                                                                                                                                                                                                                                                        |  |  |  |  |

|     | 2      | CTR              | his is the of the low-side MOSFET. Typically, a transformer is connected to this pin.                                                                                                                                                                                                                                   |  |  |  |  |

|     | 3      | μ                | This is to supply oblige of the high-side gate-drive circuit IC.  This is the connected to this pin.  This is the low-side MOGFET. Typically, a transformer is connected to this pin.  This is the high-side gate driving signal.                                                                                       |  |  |  |  |

|     | 4      | _ NC             | Nnection.                                                                                                                                                                                                                                                                                                               |  |  |  |  |

|     | 5      | NC               | No connection.                                                                                                                                                                                                                                                                                                          |  |  |  |  |

|     | q      | CON              | This pin is for a protection and enabling/disabling the controller. When the voltage of this pin is above 0.6%, the IC operation is enabled. When the voltage of this pin drops below 0.4V, gate drive signals for both MOSFETs are disabled. When the voltage of this pin increases above 5V, protection is triggered. |  |  |  |  |

|     | 7      | NC               | No connection                                                                                                                                                                                                                                                                                                           |  |  |  |  |

|     | 8      | R⊤               | This programs the switching frequency. Typically, an opto-coupler is connected to cont of the switching frequency for the output voltage regulation.                                                                                                                                                                    |  |  |  |  |

|     | 9      | cs               | This pin senses the current flowing through the low-side MOSFET. Typically, negative voltage is applied on this pin.                                                                                                                                                                                                    |  |  |  |  |

|     | 10     | SG               | This pin is the control ground.                                                                                                                                                                                                                                                                                         |  |  |  |  |

|     | 11     | NC               | No connection.                                                                                                                                                                                                                                                                                                          |  |  |  |  |

|     | 12     | LV <sub>CC</sub> | This pin is the supply voltage of the control IC.                                                                                                                                                                                                                                                                       |  |  |  |  |

|     | 13     | NC               | No connection.                                                                                                                                                                                                                                                                                                          |  |  |  |  |

|     | 14     | LO               | This is the low-side gate driving signal.                                                                                                                                                                                                                                                                               |  |  |  |  |

|     | 15     | NC               | No connection.                                                                                                                                                                                                                                                                                                          |  |  |  |  |

|     | 16     | PG               | This pin is the power ground. This pin is connected to the source of the low-side MOSFET.                                                                                                                                                                                                                               |  |  |  |  |

#### **Absolute Maximum Ratings**

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be operable above the recommended operating conditions and stressing the parts to these levels is not recommended. In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability. The absolute maximum ratings are stress ratings only.  $T_A=25^{\circ}C$  unless otherwise specified.

| Symbol                               | Parameter                                       | Min.                  | Max.             | Unit |

|--------------------------------------|-------------------------------------------------|-----------------------|------------------|------|

| $V_{HO}$                             | High-Side Gate Driving Voltage                  | V <sub>CTR</sub> -0.3 | HV <sub>CC</sub> | V    |

| $V_{LO}$                             | Low-Side Gate Driving Voltage                   | -0.3                  | LV <sub>CC</sub> | V    |

| LV <sub>CC</sub>                     | Low-Side Supply Voltage                         | -0.3                  | 25.0             | V    |

| HV <sub>CC</sub> to V <sub>CTR</sub> | High-Side V <sub>CC</sub> Pin to Center Voltage | -0.3                  | 25.0             | V    |

| V <sub>CTR</sub>                     | Center Voltage                                  | -0.3                  | J.               | V    |

| V <sub>CON</sub>                     | Control Pin Input Voltage                       | -0.3                  | LV <sub>CC</sub> | V    |

| V <sub>CS</sub>                      | Current Sense (CS) Pin Input Voltage            | _F                    | 0                | V    |

| V <sub>RT</sub>                      | R <sub>T</sub> Pin Input Voltage                | -O.                   | 5.0              | V    |

| dV <sub>CTR</sub> /dt                | Allowable Center Voltage Slew Rate              |                       | 50               | V/ns |

| P <sub>D</sub>                       | Total Power Dissipation 16-SOP                  |                       | 1.13             | W    |

| _                                    | Maximum Junction Temperature <sup>(1)</sup>     |                       | +150             | 00   |

| $T_J$                                | Recommended Operating Junction Temp at (1)      | -40                   | 4.(20)           | °C   |

| T <sub>STG</sub>                     | Storage Temperature Range                       | -55                   | +150             | °C   |

#### Note:

# Thermal Impedang

| Symbol        | Parameter                            | Value | Unit |

|---------------|--------------------------------------|-------|------|

| $\theta_{JA}$ | J Anibient Ther mal Impedance 16-SOP | 110   | °C/W |

<sup>1.</sup> The maximum value of the recommend operating junction temperature is limited by the mail shutdown.

#### **Electrical Characteristics**

$T_A \! = \! 25^{\circ} C$  and LV  $_{CC} \! = \! 17V$  unless otherwise specified.

| Symbol                          | Parameter Test Conditions                                                         |                                                                                        | Min. | Тур.  | Max.  | Unit |

|---------------------------------|-----------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|------|-------|-------|------|

| Supply Sect                     | ion                                                                               |                                                                                        |      |       |       |      |

| I <sub>LK</sub>                 | Offset Supply Leakage Current                                                     | HV <sub>CC</sub> =V <sub>CTR</sub>                                                     |      |       | 50    | μA   |

| $I_QHV_{CC}$                    | Quiescent HV <sub>cc</sub> Supply Current                                         | (HV <sub>CC</sub> UV+) - 0.1V                                                          |      | 50    | 120   | μA   |

| I <sub>Q</sub> LV <sub>CC</sub> | Quiescent LV <sub>cc</sub> Supply Current                                         | (LV <sub>CC</sub> UV+) - 0.1V                                                          |      | 100   | 200   | μA   |

| $I_0HV_{CC}$                    | Operating HV <sub>cc</sub> Supply Current (RMS Value)                             | $\begin{array}{l} f_{OSC} {=} 100 kHz, V_{CON} > 0.6V,\\ C_{Load} {=} 1nF \end{array}$ |      | 5     | 8     | mA   |

|                                 | (Nivio Value)                                                                     | No Switching, V <sub>CON</sub> < 0.4V                                                  |      | JU    | 200   | μΑ   |

| I <sub>o</sub> LV <sub>cc</sub> | Operating LV <sub>cc</sub> Supply Current (RMS Value)                             | $f_{OSC}$ =100kHz, $V_{CON}$ > 0.6V, $C_{Load}$ =1nF                                   |      | િ     | 9     | ınΛ  |

|                                 | (rivie value)                                                                     | No Switching, V <sub>CON</sub> < 0.4                                                   |      | 2     | 4     | mA   |

| UVLO Section                    | on                                                                                |                                                                                        |      |       | 11    |      |

| LV <sub>CC</sub> UV+            | LV <sub>CC</sub> Supply Under-Voltage Positive C                                  | Going Threshold (L 2 S 1)                                                              | 11.2 | 12.5  | 13.8  | V    |

| LV <sub>CC</sub> UV-            | LV <sub>CC</sub> Supply Under-Voltage Negative                                    | Going Tresi Stop)                                                                      | 3.90 | 10.00 | 11.10 | V    |

| LV <sub>CC</sub> UVH            | LV <sub>CC</sub> Supply Under-Voltage Hysteresi                                   | S                                                                                      |      | 2.5   | 10.   | V    |

| HV <sub>CC</sub> UV+            | HV <sub>CC</sub> Supply Under-Voltage Positine                                    | Goin, Thresh 1 (HVc; Start)                                                            | 8.2  | 9.2   | 10.2  | V    |

| HV <sub>CC</sub> UV-            | HV <sub>cc</sub> Supply Under-Voltage * ¬ativ                                     | Going reshold (HV <sub>3c</sub> Stop)                                                  | 7.8  | 87    | 9.6   | V    |

| HVccUVH                         | HV <sub>CC</sub> Supply Under-\( \sigma \) H, 'ere-                               |                                                                                        | 0.5  |       | V     |      |

| Oscillator &                    | Feedback Section                                                                  | 1/1/1/1/10/14                                                                          | 70   |       |       |      |

| V <sub>CONDIS</sub>             | Control Pi Jisable ash J Voltage                                                  | 0, 51                                                                                  | 0.36 | 0.40  | 0.44  | V    |

| V <sub>CONEN</sub>              | Control P Enable Threshold Voitage                                                |                                                                                        |      | 0.60  | 0.66  | V    |

| V <sub>RT</sub>                 | -I Comprte. Ushold Voltage                                                        | MICH                                                                                   | 1.5  | 2.0   | 2.5   | V    |

| fosc                            | Output C sillation Frequency R <sub>1</sub> =5 2kΩ                                |                                                                                        |      | 100   | 106   | kHz  |

| DC                              | utput Duty Cycle                                                                  |                                                                                        | 48   | 50    | 52    | %    |

| f <sub>SS</sub>                 | Internal Soft-Start Initial Frequency                                             | $f_{SS}=f_{OSC}+40kHz, R_T=5.2k\Omega$                                                 | 7    | 140   |       | kHz  |

|                                 | Internal Soft Start Time                                                          |                                                                                        | 2    | 3     | 4     | ms   |

| Output Sect                     | ion                                                                               |                                                                                        |      |       |       |      |

| I <sub>source</sub>             | Peak Sourcing Current                                                             | HV <sub>CC</sub> =17V                                                                  | 250  | 360   |       | mA   |

| I <sub>sink</sub>               | Peak Sir king Current                                                             | HV <sub>CC</sub> =17V                                                                  | 460  | 600   |       | mA   |

| tr                              | Rising Time                                                                       | 0 4.5.107 4777                                                                         |      | 65    |       | ns   |

| $t_f$                           | Falling Time                                                                      | C <sub>Load</sub> =1nF, HV <sub>CC</sub> =17V                                          |      | 35    |       | ns   |

| V <sub>HOH</sub>                | High Level of High-Side Gate Driving Signal (VHVCC-VHO)                           |                                                                                        |      |       | 1.0   | V    |

| $V_{HOL}$                       | Low Level of High-Side Gate Driving Signal                                        | I=-20mA                                                                                |      |       | 0.6   | V    |

| $V_{LOH}$                       | High Level of High-Side Gate Driving Signal (V <sub>LVCC</sub> -V <sub>LO</sub> ) |                                                                                        |      |       | 1.0   | V    |

| $V_{LOL}$                       | Low Level of High-Side Gate Driving Signal                                        |                                                                                        |      |       | 0.6   | ٧    |

#### **Electrical Characteristics** (Continued)

T<sub>A</sub>=25°C and LV<sub>CC</sub>=17V unless otherwise specified.

|                   | Parameter                                                                           | Test Conditions         | Min.  | Тур. | Max. |  |

|-------------------|-------------------------------------------------------------------------------------|-------------------------|-------|------|------|--|

| Protection        | Section                                                                             |                         |       |      |      |  |

| I <sub>OLP</sub>  | OLP Delay Current                                                                   | V <sub>CON</sub> =4V    | 3.8   | 5.0  | 6.2  |  |

| $V_{OLP}$         | OLP Protection Voltage                                                              | V <sub>CON</sub> > 3.5V | 4.5   | 5.0  | 5.5  |  |

| V <sub>OVP</sub>  | $LV_{CC}$ Over-Voltage Protection $LV_{CC} > 21V$ 21                                |                         |       |      | 25   |  |

| V <sub>AOCP</sub> | AOCP Threshold Voltage                                                              |                         | -1.0  | -0.9 | -0.8 |  |

| t <sub>BAO</sub>  | AOCP Blanking Time                                                                  |                         |       | -    |      |  |

| $V_{\text{OCP}}$  | OCP Threshold Voltage                                                               |                         | -0.64 | 0.58 | 0.52 |  |

| $t_{BO}$          | OCP Blanking Time <sup>(2)</sup>                                                    |                         | 1.0   | -    | 2.0  |  |

| t <sub>DA</sub>   | Delay Time (Low-Side) Detecting from $V_{\text{AOCP}}$ to Switch $\text{Off}^{(2)}$ |                         |       | _50  | 400  |  |

| T <sub>SD</sub>   | Thermal Shutdown Temperature <sup>(2)</sup>                                         |                         | 110   | 130  | 150  |  |

| I <sub>SU</sub>   | Protection Latch Sustain LV <sub>CC</sub> Supply Current                            | LV <sub>CC</sub> - 5V   | OP    | 100  | 150  |  |

| $V_{PRSET}$       | Protection Latch Reset LV <sub>CC</sub> Supply Voltage                              | CD                      | 5     | SI,  | 10   |  |

| Dead-Time         | Control Section                                                                     | NO                      | 0,    | NP   |      |  |

| D <sub>T</sub>    | Dead Time                                                                           | NE OUT                  |       | 350  |      |  |

| 2. These pa       | arameters, alther high rantee are not the                                           | teસ્પરુહ in production. | 7,    |      |      |  |

| 2. These pa       | arameters, alther high rantee are not to                                            | texteu in production.   | 7,    |      |      |  |

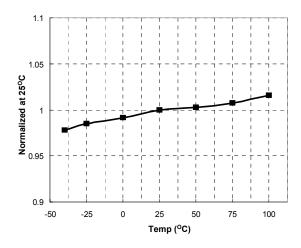

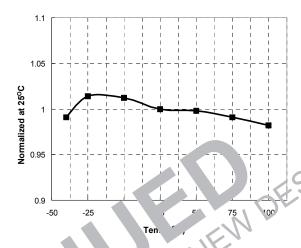

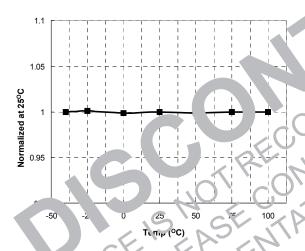

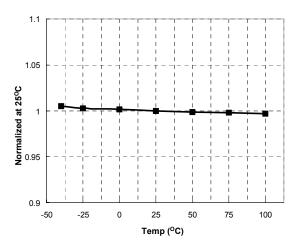

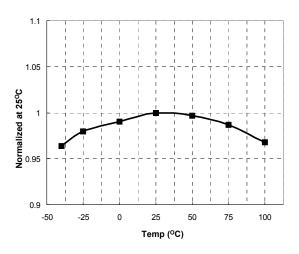

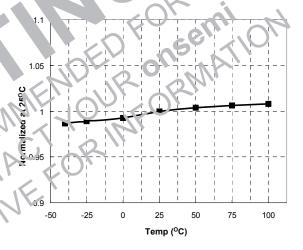

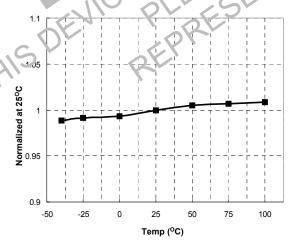

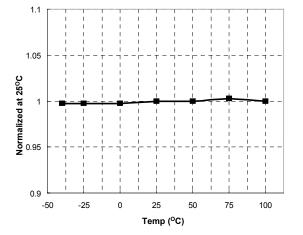

## **Typical Performance Characteristics**

These characteristic graphs are normalized at T<sub>A</sub>=25°C.

Figure 4. Low-Side MOSFET Duty Cycle vs. Temperature

Figure & Sw. hir Frequency vs. Temperature

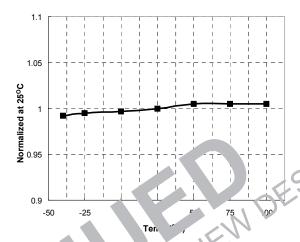

Figur .. High-Side V<sub>cc</sub> (HV<sub>cc</sub>) Start vs. Temperature

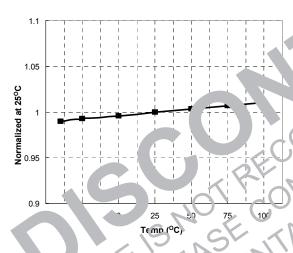

Figure 7. High-Side  $V_{\text{CC}}$  (HV<sub>CC</sub>) Stop vs. Temperature

Figure 8. Low-Side  $V_{CC}$  (LV<sub>CC</sub>) Start vs. Temperature

Figure 9. Low-Side  $V_{CC}$  (LV<sub>CC</sub>) Stop vs. Temperature

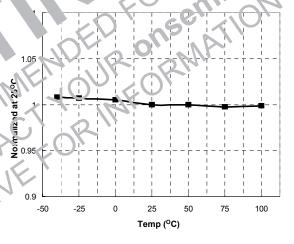

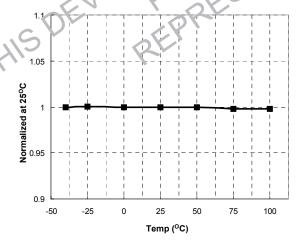

#### **Typical Performance Characteristics** (Continued)

These characteristic graphs are normalized at T<sub>A</sub>=25°C.

Figure 10. OLP Delay Current vs. Temperature

Figure 1: 7LF 'rot' stion Voltage vs. Temperature

qu' 12. LYcc OVP Voltage vs. Temperature

Figure 13. R<sub>T</sub> Voltage vs. Temperature

Figure 14. CON Pin Enable Voltage vs. Temperature

Figure 15. OCP Voltage vs. Temperature

#### **Functional Description**

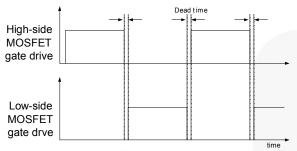

**1. Basic Operation**: FAN7621B is designed to drive high-side and low-side MOSFETs complementarily with 50% duty cycle. A fixed dead time of 350ns is introduced between consecutive transitions, as shown in Figure 16.

Figure 16. MOSFETs Gate Drive Signal

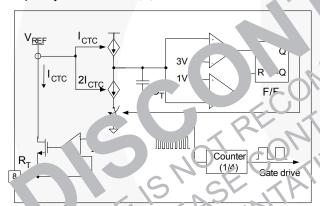

**2. Internal Oscillator**: FAN7621B employs a current-controlled oscillator, as shown in Figure 17. Internally, the voltage of  $R_T$  pin is regulated at 2V and the charging / discharging current for the oscillator capacitor,  $C_T$ , is obtained by copying the current flowing out of  $R_T$  pin ( $I_{CTC}$ ) using a current mirror. Therefore, the switchir frequency increases as  $I_{CTC}$  increases.

√ure 17. Culvent Con'rolled Oscillator

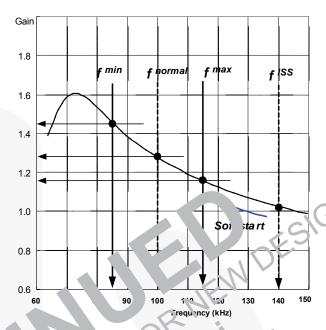

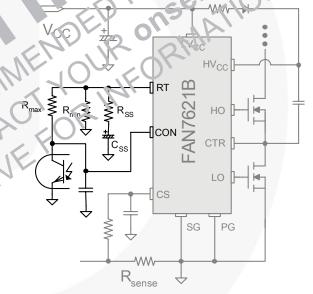

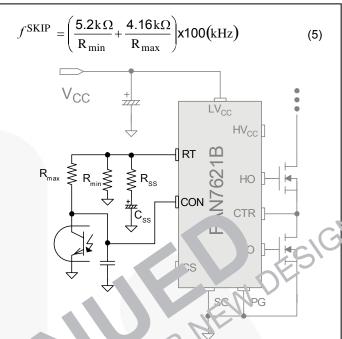

**3. Frequency Setting:** Figure 18 shows the typical voltage gain curve of a resonant converter, where the gain is inversely proportional to the switching frequency in the ZVS region. The output voltage can be regulated by modulating the switching frequency. Figure 19 shows the typical circuit configuration for  $R_T$  pin, where the opto-coupler transistor is connected to the  $R_T$  pin to modulate the switching frequency.

Fig. ຈາຍ. sonant Corverter Tາກາເລl Gain Curve

**Figure 19. Frequency Control Circuit**

The minimum switching frequency is determined as:

$$f^{\min} = \frac{5.2k\Omega}{R_{\min}} \times 100(kHz) \tag{1}$$

Assuming the saturation voltage of opto-coupler transistor is 0.2V, the maximum switching frequency is determined as:

$$f^{\max} = (\frac{5.2k\Omega}{R_{\min}} + \frac{4.68k\Omega}{R_{\max}}) \times 100 (kHz)$$

(2)

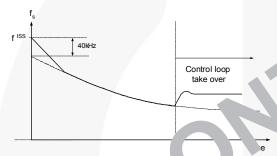

To prevent excessive inrush current and overshoot of output voltage during startup, increase the voltage gain of the resonant converter progressively. Since the voltage gain of the resonant converter is inversely

proportional to the switching frequency, the soft-start is implemented by sweeping down the switching frequency from an initial high frequency ( $f^{ISS}$ ) until the output voltage is established. The soft-start circuit is made by connecting R-C series network on the R<sub>T</sub> pin, as shown in Figure 19. FAN7621B also has an internal soft-start for 3ms to reduce the current overshoot during the initial cycles, which adds 40kHz to the initial frequency of the external soft-start circuit, as shown in Figure 20. The initial frequency of the soft-start is given as:

$$f^{ISS} = (\frac{5.2k\Omega}{R_{\min}} + \frac{5.2k\Omega}{R_{SS}}) \times 100 + 40 \ (kHz)$$

(3)

It is typical to set the initial (soft-start) frequency of two  $\sim$  three times the resonant frequency ( $f_O$ ) of the resonant network.

The soft-start time is three to four times the RC time constant. The RC time constant is as follows:

$$T_{SS} = R_{SS} \cdot C_{SS} \tag{4}$$

Figure 20. Frequency Jep. 7 of \$ t-Start

**4. Control Pin**: The F. V7621P has a control pin for protection, cycle ... ping and renote on of a Figure 21 shows the internal block diagram or control pin.

Figure 21. Internal Block of Control Pin

**Protection**: When the control pin voltage exceeds 5V, protection is triggered. Detailed applications are described in the protection section.

**Pulse Skipping**: FAN7621B stops switching when the control pin voltage drops below 0.4V and resumes switching when the control pin voltage rises above 0.6V. To use pulse-skipping, the control pin should be connected to the opto-coupler collector pin. The frequency that causes pulse skipping is given as:

Figure 22. Control Pin Configuration for Pulse Skipping

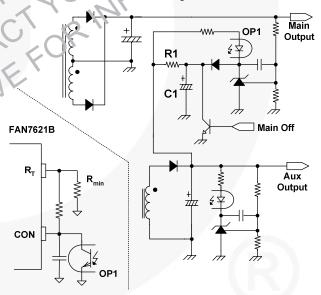

Remote On / On: When an auxiliary power supply is used for standby, the main power stage using FAN70213 can be snot down by pulling down the control provoltage as shown in Figure 23. R1 and C1 are used to ensure soft-start when switching resumes.

Figure 23. Remote On / Off Circuit

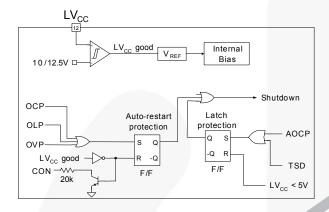

**5. Protection Circuits**: The FAN7621B has several self-protective functions, such as Overload Protection (OLP), Over-Current Protection (OCP), Abnormal Over-Current Protection (AOCP), Over-Voltage Protection (OVP), and Thermal Shutdown (TSD). OLP, OCP, and OVP are auto-restart mode protections; while AOCP and TSD are latch-mode protections, as shown in Figure 24.

**Auto-Restart Mode Protection**: Once a fault condition is detected, switching is terminated and the MOSFETs remain off. When LV<sub>CC</sub> falls to the LV<sub>CC</sub> stop voltage of 10.0V, the protection is reset. FAN7621B resumes normal operation when LV<sub>CC</sub> reaches the start voltage of 12.5V.

**Latch-Mode Protection**: Once this protection is triggered, switching is terminated and the gate output signals remain off. The latch is reset only when  $LV_{CC}$  is discharged below 5V.

Figure 24. Protection Blocks

Current Sensing Using Resistor: FAN7621B the sensing current as a negative voltage, as showing Filipse 25 and Figure 26. Half-wave sensing resistor, the fill-wave sensing has less switching noise in the sensing signal.

Figure 25. Half-Wave Sensing

Figure 26. Figure 36. Figure 26. Figure 36. Figure 36.

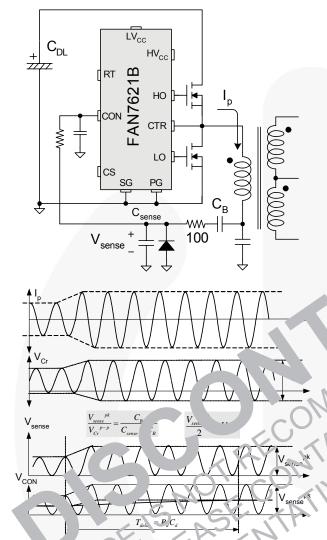

Current Sensing ''sin, '' sonant spacifor /oitage: For high-power aptications, when the sensing using a resistor may be all a due to the severe power dissipation in the resistor. In that case, indirect current senting using a transfer of the severe power dissipation in the resistor. In that case, indirect current senting using a transfer of the resonant capacitor voltage can be a cool of the resonant capacitor voltage ( $V_{\rm p}^{\rm pp}$ ) is proportion at to the resonant current the primary side ( $I_{\rm p}^{\rm pp}$ ) as.

$$V_{Cr}^{p-p} = \frac{I_{2}}{2\pi} \frac{I_{2}}{I_{C}}$$

(6)

To minimize power dissipation, a capacitive voltage divider is generally used for capacitor voltage sensing, as shown in Figure 27.

ure 27. Current Seasing Using Resonant Capacitor Voltage

**5.1 Over Current Protection (OCP):** When the sensing pin voltage drops below -C.6V, OCP is triggered and the MOSFETs remain off. This protection has a shutdown time delay of 1.5µs to prevent premature shutdown during startup.

**5.2 Abnormal Over-Current Protection**: **(AOCP)**: If the secondary rectifier diodes are shorted, large current with extremely high di/dt can flow through the MOSFET before OCP or OLP is triggered. AOCP is triggered without shutdown delay when the sensing pin voltage drops below -0.9V. This protection is latch mode and reset when LV<sub>CC</sub> is pulled down below 5V.

5.3 Overload Protection (OLP): Overload is defined as the load current exceeding its normal level due to an unexpected abnormal event. In this situation, the protection circuit should trigger to protect the power supply. However, even when the power supply is in the normal condition, the overload situation can occur during the load transition. To avoid produre triggering of protection, the overload prot ion coult should be designed to trigger only after a sprified time to determine whether it is a transic 'sity tion or a true overload situation. Fig. 9.21 show . typicai cverload protection circuit. v s sing the resonant capacitor voltage on the controllin, a serioad protection can be implemented. 'sing it in a constant, shutdown delay can be a n in nduc . The voltage obtained on the avir , nir COI.

$$V_{c} = \frac{c_{B}}{c_{B} + C_{c}} V_{C_{c}} - V_{C_{c}}$$

(7)

where  $V_{C_1}^{(n)}$  is the amplitude of the resonant capacitor voltage.

- 5.4 Over-Voltage Protection: (OVP): When the LV $_{CC}$  reaches 25V, DVP is triggered. This protection is used when auxiliary winding of the transformer to supply V $_{CC}$  to the controller is utilized.

- **5.5 The mal Shutdown (TSD)**: If the temperature of the junction exceeds approximately 130°C, the thermal shutdown triggers.

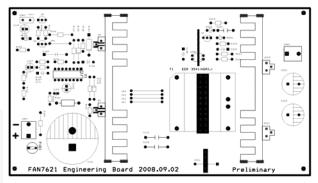

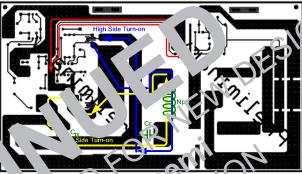

6. PCB Layout Guideline: Duty imbalance problems may occur due to the radiated noise from main transformer, the inequality of the secondary-side leakage inductances of main transformer, and so on. Among them, it is one of the dominant reasons that the control components in the vicinity of R<sub>T</sub> pin are enclosed by the primary current flow pattern on PCB layout. The direction of the magnetic field on the components caused by the primary current flow is changed when the high-and-low side MOSFET turns on by turns. The magnetic fields with opposite direction from each other induce a current through, into, or out of the R<sub>T</sub> pin, which makes the turnon duration of each MOSFET different. It is strongly recommended to separate the control components in the vicinity of R<sub>T</sub> pin from the primary current flow pattern on PCB layout. Figure 28 shows an example for the dutybalanced case. The yellow and blue lines show the primary current flows when the lower-side and higherside MOSFETs turns on, respectively. The primary current does not enclose any component of controller.

In addition, it is helpful to reduce the duty imbalance to make the loop configured between CON pin and optocoupler as small as possible, as shown in the red line in Figure 28.

Figure 28. Example for Duty Ealancing

# **Typical Application Circuit (Half-Bridge LLC Resonant Converter)**

| Application | Device   | Input Voltage Range                             | Rated Output Power | Output Voltage (Rated Current) |

|-------------|----------|-------------------------------------------------|--------------------|--------------------------------|

| LCD TV      | FAN7621B | 390V <sub>DC</sub><br>(340~400V <sub>DC</sub> ) | 192W               | 24V-8A                         |

#### **Features**

- High efficiency ( >94% at 400V<sub>DC</sub> input)

- Reduced EMI noise through zero-voltage-switching (ZVS)

- Enhanced system reliability with various protection functions

Figure 29. Typical Application Circuit

#### **Typical Application Circuit** (Continued)

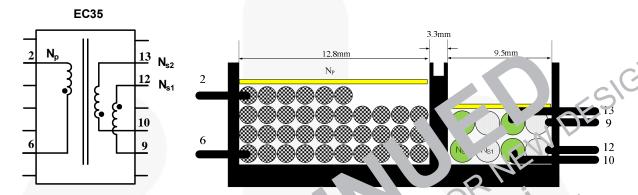

Usually, LLC resonant converters require large leakage inductance value. To obtain a large leakage inductance, sectional winding method is used.

Core: EC35 (Ae=106 mm²)

Bobbin: EC35 (Horizontal)

Transformer Model Number: SNX-2468-1

Figure 30. Transorme Son Sruction

|                 | Pins (S → F) | W. Turns                | Note            |

|-----------------|--------------|-------------------------|-----------------|

| N <sub>p</sub>  | 6 → 2        | 784 88 (Li∠ Wire) 35    |                 |

| N <sub>s1</sub> | 12 → 9       | 0.( p×234 (Litz Wire) 4 | Bifilar Winding |

| N <sub>s2</sub> | 10 → 1       | ∪.08φ×234 (Litz Wire) 4 | Bifilar Winding |

| Pins                                           | Specifications | Remark                              |

|------------------------------------------------|----------------|-------------------------------------|

| Prii. γ-、'e Inuuctance (L <sub>p</sub> ) 2 – 6 | 550μH ± 10%    | 100kHz, 1V                          |

| P. rary- de Effective Leakage () 2 -0          | 110μH ± 10%    | Short one of the secondary windings |

For more detailed information regarding the transformer, visit <a href="http://www.santronics-usa.com/documents.html">http://www.santronics-usa.com/documents.html</a> or contact sales @santronics-usa.com or +1-408-734-1878 (Sunnyvale, California USA).

TERN RECOMMENDATION

# NOTES:

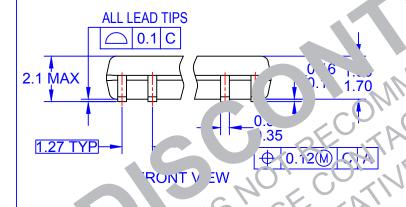

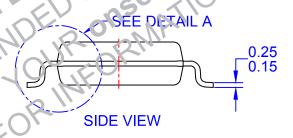

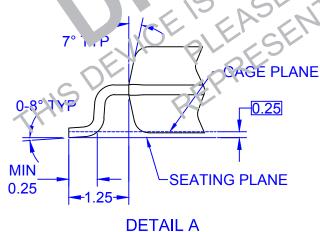

- A. CONFORMS TO EIAJ EDR-7320 REGISTRATION, ESTABLISHED IN DECEMBER, 1998.

B. DIMENSIONS ARE IN MILLIMETERS.

- C. DIMENSIONS ARE EXCLUSIVE OF BURRS, MOLD FLASH, AND TIE BAR EXTRUSIONS.

- D. DRAWING FILENAME: MKT-M16Drev5

ON Semiconductor and the are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at <a href="https://www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor and severally, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify an

#### **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor 19521 E. 32nd Pkwy, Aurora, Colorado 80011 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com

USA/Canada

Europe, Middle East and Africa Technical Support:

Phone: 421 33 790 2910

Japan Customer Focus Center

Phone: 81-3-5817-1050

N. American Technical Support: 800-282-9855 Toll Free

ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative